Hello,

I want to communicate with an External IC using SCI and DMA i.e. both Write to and Read from the IC.

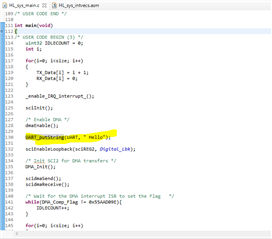

When I enable the SCI loopback, then I am able to Write Data and Read the same data back.

Here is the code below

/** @file HL_sys_main.c

* @brief Application main file

* @date 11-Dec-2018

* @version 04.07.01

*

* This file contains an empty main function,

* which can be used for the application.

*/

/*

* Copyright (C) 2009-2018 Texas Instruments Incorporated - www.ti.com

*

*

* Redistribution and use in source and binary forms, with or without

* modification, are permitted provided that the following conditions

* are met:

*

* Redistributions of source code must retain the above copyright

* notice, this list of conditions and the following disclaimer.

*

* Redistributions in binary form must reproduce the above copyright

* notice, this list of conditions and the following disclaimer in the

* documentation and/or other materials provided with the

* distribution.

*

* Neither the name of Texas Instruments Incorporated nor the names of

* its contributors may be used to endorse or promote products derived

* from this software without specific prior written permission.

*

* THIS SOFTWARE IS PROVIDED BY THE COPYRIGHT HOLDERS AND CONTRIBUTORS

* "AS IS" AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT

* LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR

* A PARTICULAR PURPOSE ARE DISCLAIMED. IN NO EVENT SHALL THE COPYRIGHT

* OWNER OR CONTRIBUTORS BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL,

* SPECIAL, EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT

* LIMITED TO, PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES; LOSS OF USE,

* DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON ANY

* THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT

* (INCLUDING NEGLIGENCE OR OTHERWISE) ARISING IN ANY WAY OUT OF THE USE

* OF THIS SOFTWARE, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

*

*/

/* USER CODE BEGIN (0) */

/* USER CODE END */

/* Include Files */

#include "HL_sys_common.h"

/* USER CODE BEGIN (1) */

#include "HL_system.h"

#include "HL_sci.h"

#include "HL_sys_pmu.h"

#include "HL_sys_dma.h"

#include "HL_sys_vim.h"

/* USER CODE END */

/** @fn void main(void)

* @brief Application main function

* @note This function is empty by default.

*

* This function is called after startup.

* The user can use this function to implement the application.

*/

/* USER CODE BEGIN (2) */

#define size 20U

#define SCI2_TX_ADDR ((uint32_t)(&(sciREG2->TD)) + 3)

#define SCI2_RX_ADDR ((uint32_t)(&(sciREG2->RD)) + 3)

#define DMA_SCI2_TX_CH DMA_REQ41

#define DMA_SCI2_RX_CH DMA_REQ40

#define SCI_SET_TX_DMA (1<<16)

#define SCI_SET_RX_DMA (1<<17)

#define SCI_SET_RX_DMA_ALL (1<<18)

/* dma control packet configuration stack */

uint32 DMA_Comp_Flag;

uint32 DMA_TX_Counter;

uint32 DMA_RX_Counter;

#pragma SET_DATA_SECTION(".sharedRAM")

uint8 TX_Data[size] = {0};

uint8 RX_Data[size] = {0};

#pragma SET_DATA_SECTION()

int main(void);

void DMA_Init(void);

void scidmaInit();

void scidmaSend();

void scidmaReceive();

void Update_DMA_Comp_Flag(uint32 channel);

/* USER CODE END */

int main(void)

{

/* USER CODE BEGIN (3) */

uint32 IDLECOUNT = 0;

_enable_IRQ_interrupt_();

sciInit();

sciEnableLoopback(sciREG2, Digital_Lbk);

/* Enable DMA */

dmaEnable();

/* Init SCI2 for DMA transfers */

DMA_Init();

/* Enable Interrupt after reception of data */

dmaEnableInterrupt(DMA_CH0, BTC, DMA_INTA);

scidmaSend();

dmaEnableInterrupt(DMA_CH1, BTC, DMA_INTA);

scidmaReceive();

/* Wait for the DMA interrupt ISR to set the Flag */

while(DMA_Comp_Flag != 0x55AAD09E){

IDLECOUNT++;

}

while (1);

/* USER CODE END */

//return 0;

}

/* USER CODE BEGIN (4) */

void DMA_Init(void)

{

/* Init SCI3 for DMA transfers */

scidmaInit();

}

/** @fn void scidmaInit(short mode)

* @brief Initialize the SCI and DMA to tranfer SCI data via DMA

* @note This function configures the SCI to trigger a DMA request when the SCI TX is complete.

*/

void scidmaInit()

{

dmaReqAssign(DMA_CH0, DMA_SCI2_TX_CH);

dmaReqAssign(DMA_CH1, DMA_SCI2_RX_CH);

/* Reset the Flag */

DMA_Comp_Flag = 0x55AAD09E;

/* Channel 40 - Enable the VIM channel in HalCoGen to include dmaBTCAInterrupt function */

vimChannelMap(40, 40, &dmaBTCAInterrupt);

/* Enable VIM DMA BTCA interrupt to CPU on SCI2 transfer complete */

vimEnableInterrupt(40, SYS_IRQ);

} /* scidmaInit */

/** @fn void scidmaSend(char *source_address, short mode)

* @brief Initialize the SCI and DMA to tranfer SCI data via DMA

* @note This function configures the SCI to trigger a DMA request when the SCI TX is complete.

*

* This function configures the DMA in single buffer or multibuffer mode.

* In single buffer mode (0) the DMA moves each Byte to the SCI tranmit register when request is set.

* In multi buffer mode (1) the DMA moves 4 Bytes to the SCI transmit buffer when the request is set.

*/

void scidmaSend()

{

g_dmaCTRL g_dmaCTRLPKT;

int i;

for(i=0; i<size; i++)

{

TX_Data[i] = i + 1;

}

/* Wait for the DMA to complete any existing transfers */

while(DMA_Comp_Flag != 0x55AAD09E);

/* Reset the Flag to not Done*/

DMA_Comp_Flag = ~0x55AAD09E;

/* - Populate dma control packets structure */

g_dmaCTRLPKT.CHCTRL = 0; /* channel control */

g_dmaCTRLPKT.ELCNT = 1; /* element count */

g_dmaCTRLPKT.ELDOFFSET = 0; /* element destination offset */

g_dmaCTRLPKT.ELSOFFSET = 0; /* element source offset */

g_dmaCTRLPKT.FRDOFFSET = 0; /* frame destination offset */

g_dmaCTRLPKT.FRSOFFSET = 0; /* frame source offset */

g_dmaCTRLPKT.PORTASGN = PORTA_READ_PORTB_WRITE; /* PORTA_READ_PORTB_WRITE */

g_dmaCTRLPKT.RDSIZE = ACCESS_8_BIT; /* read size */

g_dmaCTRLPKT.WRSIZE = ACCESS_8_BIT; /* write size */

g_dmaCTRLPKT.TTYPE = FRAME_TRANSFER ; /* transfer type */

g_dmaCTRLPKT.ADDMODERD = ADDR_INC1; /* address mode read */

g_dmaCTRLPKT.ADDMODEWR = ADDR_FIXED; /* address mode write */

g_dmaCTRLPKT.AUTOINIT = AUTOINIT_OFF; /* autoinit */

g_dmaCTRLPKT.SADD = (uint32)TX_Data;

g_dmaCTRLPKT.DADD = SCI2_TX_ADDR;

g_dmaCTRLPKT.FRCNT = size;

/* - setting dma control packets for transmit */

dmaSetCtrlPacket(DMA_CH0, g_dmaCTRLPKT);

/* - setting the dma channel to trigger on h/w request */

dmaSetChEnable(DMA_CH0, DMA_HW);

/* Enable TX DMA */

sciREG2->SETINT = SCI_SET_TX_DMA;

} /* scidmaSend */

/** @fn void scidmaReceive(char *source_address)

*/

void scidmaReceive()

{

g_dmaCTRL g_dmaCTRLPKT;

/* Wait for the DMA to complete any existing transfers */

while(DMA_Comp_Flag != 0x55AAD09E);

/* Reset the Flag to not Done*/

DMA_Comp_Flag = ~0x55AAD09E;

/* - Populate dma control packets structure */

g_dmaCTRLPKT.CHCTRL = 0; /* channel control */

g_dmaCTRLPKT.ELCNT = 1; /* element count */

g_dmaCTRLPKT.ELDOFFSET = 0; /* element destination offset */

g_dmaCTRLPKT.ELSOFFSET = 0; /* element source offset */

g_dmaCTRLPKT.FRDOFFSET = 0; /* frame destination offset */

g_dmaCTRLPKT.FRSOFFSET = 0; /* frame source offset */

g_dmaCTRLPKT.PORTASGN = PORTB_READ_PORTA_WRITE; /* PORTB_READ_PORTA_WRITE */

g_dmaCTRLPKT.RDSIZE = ACCESS_8_BIT; /* read size */

g_dmaCTRLPKT.WRSIZE = ACCESS_8_BIT; /* write size */

g_dmaCTRLPKT.TTYPE = FRAME_TRANSFER ; /* transfer type */

g_dmaCTRLPKT.ADDMODERD = ADDR_FIXED; /* address mode read */

g_dmaCTRLPKT.ADDMODEWR = ADDR_INC1; /* address mode write */

g_dmaCTRLPKT.AUTOINIT = AUTOINIT_OFF; /* autoinit */

g_dmaCTRLPKT.SADD = SCI2_RX_ADDR;

g_dmaCTRLPKT.DADD = (uint32)RX_Data;

g_dmaCTRLPKT.FRCNT = size;

/* - setting dma control packets for transmit */

dmaSetCtrlPacket(DMA_CH1, g_dmaCTRLPKT);

/* - setting the dma channel to trigger on h/w request */

dmaSetChEnable(DMA_CH1, DMA_HW);

sciEnableNotification(sciREG2, SCI_RX_INT);

/* Enable RX DMA */

sciREG2->SETINT |= SCI_SET_RX_DMA;

} /* scidmaReceive */

/** @fn void Update_DMA_Comp_Flag()

* @brief Switch the DMA complete flag to done and disable the SCI2 TX DMA interrupt

* @note This function needs to be called by dmaGroupANotification in notification.c

*/

void Update_DMA_Comp_Flag(uint32 channel)

{

/* Set the Flag to Done*/

DMA_Comp_Flag = 0x55AAD09E;

if(channel == DMA_CH0)

{

/* Disable TX DMA Interrupt */

sciREG2->CLEARINT = SCI_SET_TX_DMA;

DMA_TX_Counter++;

}

else if(channel == DMA_CH1)

{

/* Disable RX DMA Interrupt */

sciREG2->CLEARINT = SCI_SET_RX_DMA;

DMA_RX_Counter++;

}

}

/* USER CODE END */

But the same does not work when I read back without the loopback.

In the examples too, I could see that Either "SCI loopback is used" or "Tx and Rx is done on different Hardware SCI units".

Can't the same Hardware be used for both Transmitting and Receiving??

Kind Regards