Hiving questions about the state of the DMA engine after a data transfer.

The context is the following:

In SPI mode.

SPI2 TX Master clock and SIMO connected to SPI3 RX slave.

Clock is 15 Mbps : VClk /5

SP2 TX is using channel 3.

SP3 RX is using channel 2.

Both FIFO are bypassed.

No other DMA are active.

SPI character are 16 bits and no CS are used.

SPI3 RX is made DMA ready to received data.

SPI2 TX is enabled sending its request to the DMA controller.

Both system are using the BTC interrupt.

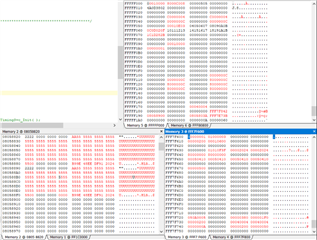

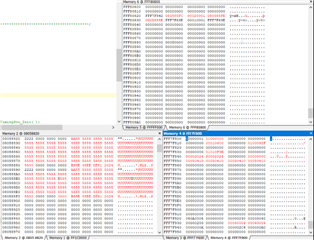

First full transfer works: both BTC interrupts comes and no data is missing in memory.

In this context I also have a CRC64 at end of frame for verification purpose.

Q1) First question is despite to full completion of the DMA transfer, why is the PEND register indicating a pending request on the TX channel?

Q2) Why are channel 14 & 15 showing pending requests, yet not enabled and involved in this transfer?

Q3) Why is DMA channel 2 (SPI3 RX) active control packet showing count 2 instead of 1?

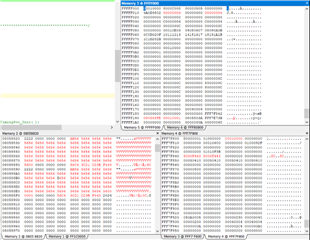

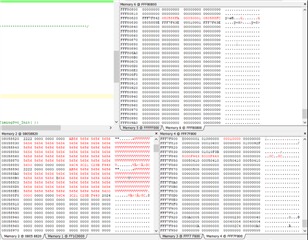

This is the following second transfer results.

The RX BTC is missing. The transmission completed. The RX results buffer shows a missing 0x5656 entry.

Q4) Why is the first transfer always working and the similar second one is missing a character at about same location in the transfer?

- Here the scope shows no missing data and all data are sent. Exactly one character is missing which lead the missing RX BTC interrupt.

- Doesn't seam to be noise on line all data before and following the missing character are OK.

I am ready to answer other settings question, but keep in mind that it is working at 7.5Mbps despite the strange DMA states.