Hi all

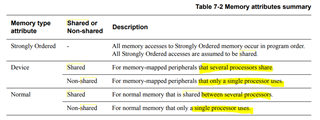

1.There is a background region including the whole SRAM from 0x0800_0000 to 0x0807_FFFF. The attributes of this region is "MPU_PRIV_RW_USER_RO_NOEXEC | MPU_NORMAL_OIWBNOWA_NONSHARED".

2. There is a region 6 which from 0x0800_0000 to 0x0801_0000. The attributes of this region is "MPU_PRIV_RW_USER_RO_NOEXEC | MPU_NORMAL_OIWBNOWA_NONSHARED".

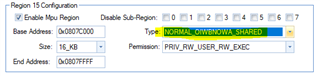

3. Also, I have a overlay region 4 which from 0x0800_0000 to 0x0803_0000, The attributes of this region is "MPU_PRIV_RW_USER_RO_NOEXEC | MPU_NORMAL_OIWBNOWA_SHARED".

The question is that when I change region 6 from nonshared to shared, the mcu will keep rebooting. but whty?

Best Wish

Li