Hi experts,

The Flash_read API has three critical parameters: offset, buf pointer and length. I want to know the constraints for offset and length. From my test, if the length/offset is not a multiple of 4, the read-out data will be wrong.

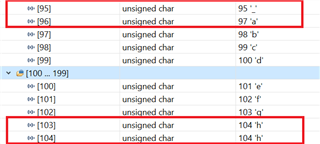

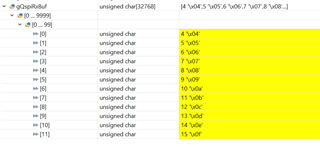

When offset = 0 and the length = 105:

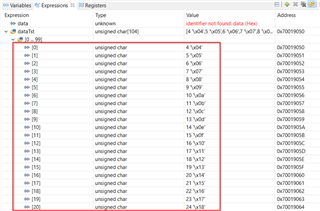

The actual Flash data is:

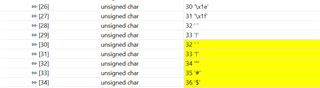

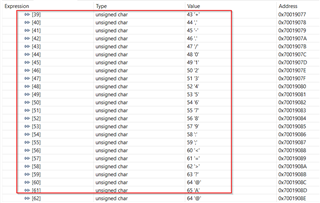

When offset = 2 and the length = 104. First 62-byte all wrong:

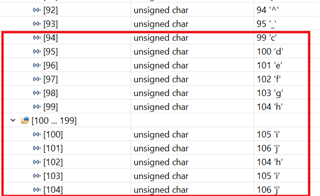

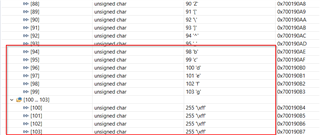

And the last 10 bytes are also wrong:

CPU directly read doesn't have this problem. Please give your comments on this problem.

Best Regards,

Will