Other Parts Discussed in Thread: HALCOGEN, TMS570LS3137

Hi Team,

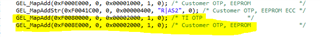

I am using the Flash library F021 from https://www.ti.com/tool/HERCULES-F021FLASHAPI for TMS570LC4357 HDK.

During initialization of Flash library the function Fapi_initializeFlashBanks() returns Fapi_Error_OtpChecksumMismatch.

I am using F021_API_CortexR4_BE.lib.

Fapi_initializeFlashBanks() is called with 160MHz. The system clock is also set to 160MHz.

If F021_API_CortexR4_BE_L2FMC.lib or F021_API_CortexR4_BE_L2FMC_V3D16 is used, the call to function Fapi_initializeFlashBanks() hangs.

Could you kindly guide to solve the issue?