Other Parts Discussed in Thread: HALCOGEN

Hello Team,

I'm posting on behalf of my customer. Please see inquiry below:

I'm getting errors when attempting to debug a custom board with the RM57 using the XDS110 debug probe.

Details:

- Testing using Hello World program

- JTAG test connection is successful

- If a release build is loaded then the MCU can be programmed with another build with no errors

- If a debug build is loaded and I attempt to load a program then I get this error:

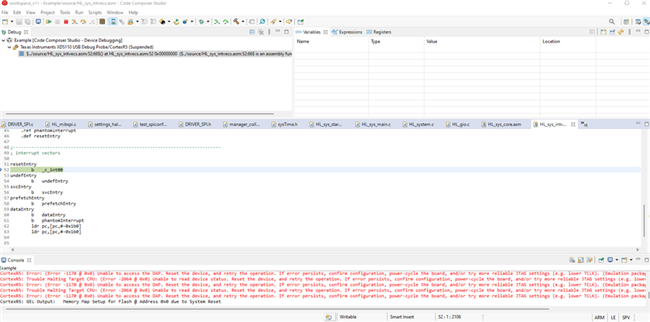

"[ERROR] Dap: Error connecting to the target: (Error -1170 @ 0x0) Unable to access the DAP. Reset the device, and retry the operation. If error persists, confirm configuration, power-cycle the board, and/or try more reliable JTAG settings (e.g. lower TCLK). (Emulation package 9.7.0.00213)".

After pressing the Warm Reset the warm reset button at the right time, the log shows:

"CortexR5: GEL Output: Memory Map Setup for Flash @ Address 0x0CortexR5: GEL Output: Memory Map Setup for Flash @ Address 0x0 due to System Reset"

- Then if I hit resume in the debugger, this starts repeating:

"CortexR5: Error: (Error -1170 @ 0x0) Unable to access the DAP. Reset the device, and retry the operation. If error persists, confirm configuration, power-cycle the board, and/or try more reliable JTAG settings (e.g. lower TCLK). (Emulation package 9.6.0.00172)

Additional troubleshooting steps:

- I looked at this webpage: https://software-dl.ti.com/ccs/esd/documents/ccs_debugging_jtag_connectivity_issues.html but the link for "A procedure to try and unlock a Hercules device is described in this e2e forum thread." gives the error that the page is not found.

- I checked my voltage supervisors and they do not appear to be triggering a power reset

- Reduced the JTAG clock speed to the minimum (100 kHz)

- Launch target configuration appears to connect successfully then when I hit run, it repeats errors -2064 and -1170

I'm not sure if there's some initial unlocking procedure to be done with new chips to get them in debug mode (I know this is true for other MCUs but I didn't find it for Hercules). Are there initial programming instructions for new chips? I don't think it's a power issue as the voltage supervisors aren't triggering and the JTAG test is successful. If it is a hardware error, then what could it be?

JTAG Test Connection Log:

[Start: Texas Instruments XDS110 USB Debug Probe]

Execute the command:

%ccs_base%/common/uscif/dbgjtag -f %boarddatafile% -rv -o -S integrity

[Result]

-----[Print the board config pathname(s)]------------------------------------

C:\Users\Lesley\AppData\Local\TEXASI~1\CCS\

ccs1110\0\0\BrdDat\testBoard.dat

-----[Print the reset-command software log-file]-----------------------------

This utility has selected a 100- or 510-class product.

This utility will load the adapter 'jioxds110.dll'.

The library build date was 'Dec 8 2021'.

The library build time was '11:16:32'.

The library package version is '9.6.0.00172'.

The library component version is '35.35.0.0'.

The controller does not use a programmable FPGA.

The controller has a version number of '5' (0x00000005).

The controller has an insertion length of '0' (0x00000000).

This utility will attempt to reset the controller.

This utility has successfully reset the controller.

-----[Print the reset-command hardware log-file]-----------------------------

The scan-path will be reset by toggling the JTAG TRST signal.

The controller is the XDS110 with USB interface.

The link from controller to target is direct (without cable).

The software is configured for XDS110 features.

The controller cannot monitor the value on the EMU[0] pin.

The controller cannot monitor the value on the EMU[1] pin.

The controller cannot control the timing on output pins.

The controller cannot control the timing on input pins.

The scan-path link-delay has been set to exactly '0' (0x0000).

-----[Perform the Integrity scan-test on the JTAG IR]------------------------

This test will use blocks of 64 32-bit words.

This test will be applied just once.

Do a test using 0xFFFFFFFF.

Scan tests: 1, skipped: 0, failed: 0

Do a test using 0x00000000.

Scan tests: 2, skipped: 0, failed: 0

Do a test using 0xFE03E0E2.

Scan tests: 3, skipped: 0, failed: 0

Do a test using 0x01FC1F1D.

Scan tests: 4, skipped: 0, failed: 0

Do a test using 0x5533CCAA.

Scan tests: 5, skipped: 0, failed: 0

Do a test using 0xAACC3355.

Scan tests: 6, skipped: 0, failed: 0

All of the values were scanned correctly.

The JTAG IR Integrity scan-test has succeeded.

-----[Perform the Integrity scan-test on the JTAG DR]------------------------

This test will use blocks of 64 32-bit words.

This test will be applied just once.

Do a test using 0xFFFFFFFF.

Scan tests: 1, skipped: 0, failed: 0

Do a test using 0x00000000.

Scan tests: 2, skipped: 0, failed: 0

Do a test using 0xFE03E0E2.

Scan tests: 3, skipped: 0, failed: 0

Do a test using 0x01FC1F1D.

Scan tests: 4, skipped: 0, failed: 0

Do a test using 0x5533CCAA.

Scan tests: 5, skipped: 0, failed: 0

Do a test using 0xAACC3355.

Scan tests: 6, skipped: 0, failed: 0

All of the values were scanned correctly.

The JTAG DR Integrity scan-test has succeeded.

[End: Texas Instruments XDS110 USB Debug Probe]

Regards,

Renan