Part Number: AM2732-Q1

Other Parts Discussed in Thread: AM2732

Howdy. I want to measure the amount of time it takes for this MCU to power up and be ready to communicate with an Ethernet PHY.

In a test board, this MCU is connected to a DP83TC812 PHY. I am trying to do TC10 wakeup/sleep measurements on this board. One of the measurements involves measuring the time it takes for the MCU to boot up and configure the PHY to be a master so it can link to a remote PHY.

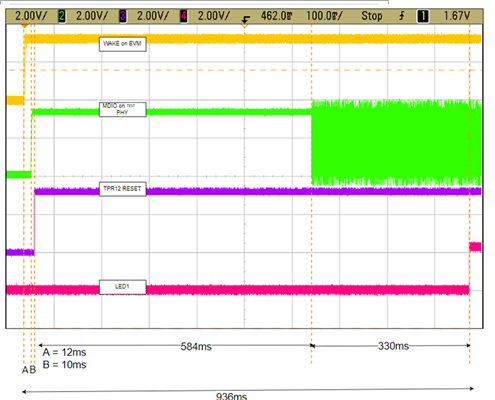

- It takes 584ms to see any activity on the MDIO data line. In other words, it takes 584ms from the RESET signal going HIGH to show any data on the MDIO line. I assume this is the point at which the MCU is powered on and ready to communicate to the PHY, correct? Is this time interval too long?

- It takes 330ms for the PHY to be configured as a master(It starts off as slave) and link with another PHY. This interval of 330ms shows a stream of MDIO data being sent to the PHY and at some point of this data, I assume a master configuration signal is being sent. Is there a way to check when this specific configuration signal is sent? I assume there are other instructions being sent besides the master configuration.