Part Number: TMS570LS1114

I have asked the difference between 1BIT ECC of Flash and 1BIT ECC of Sram on E2E before. Due to the characteristics of Flash itself, the corrected data cannot be written to Flash, that is, the data on the original Flash address cannot be corrected and written, but the data corrected by Sram is automatically written. The message in the following picture is returned.

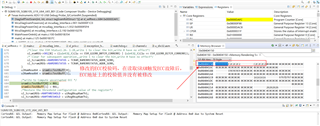

However, during the test, I modified the data on the ECC address and then read the corresponding SRAM data, which triggered the 1BIT ECC fault. However, the ECC check code on the ECC address was not corrected, and the previous wrong ECC code was still kept. At this time, when the SRAM data was triggered to read, the 1BIT ECC fault was not triggered. That is, the ECC check code is corrected, but why I see the memory data is still wrong, as shown in the picture below;

Why is the value of the ECC check code on the memory address displayed as ????

Only when the SRAM data is rewritten, the ECC check code on the corresponding address will be updated to the correct value, as shown in the figure below. Therefore, I have a question about how to correct the ECC of SRAM.