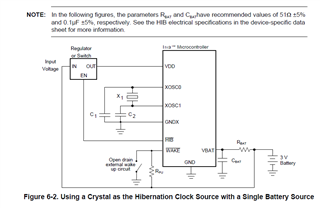

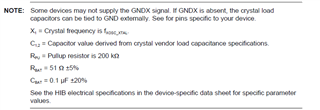

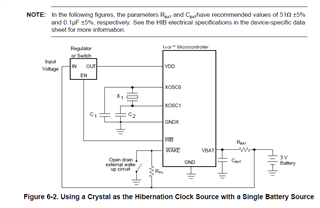

We can measure the power consumption in hibernation 43 uA at VBAT. As we understand we cannot control the pins and set them during hibernation. Why would the hibernation module consume so much power, we need RTC and we use externa crystal 32kHz, but still according to the datasheet the typical power consumption is 1.29 uA. Any tips are appreciated.

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.