Part Number: TM4C129XNCZAD

Hi TI Experts,

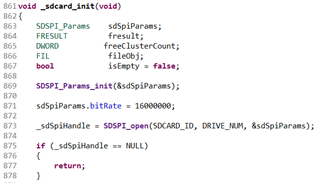

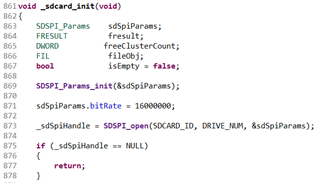

Our TM4C operates at 120MHz, we fill in the 16000000 in the code,

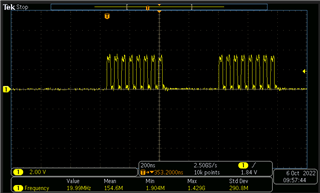

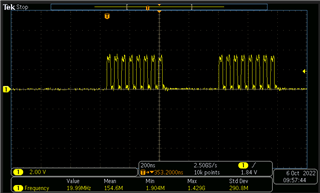

But the measured value is 20MHz, we don't know why?

Please advise, thank you.

Ray Yang

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Part Number: TM4C129XNCZAD

Hi TI Experts,

Our TM4C operates at 120MHz, we fill in the 16000000 in the code,

But the measured value is 20MHz, we don't know why?

Please advise, thank you.

Ray Yang

Hello Ray,

The SSI clock must be an even integer divider from the system clock frequency so if you are running at 120MHz system clock then the two divider options around 16 MHz are 15 MHz (divide by 8) and 20MHz (divide by 6). Because you selected 16 MHz, the TivaWare API assumes you need 16MHz or faster, so it configures the SSI bus to be at 20MHz which exceeds the ask of 16MHz.

Because the divider has to be even, using the PLL at 160MHz for an 80MHz system clock still would not get you to 16 MHz because that would require an odd divider which is not possible. So you won't be able to get an exact 16MHz output for the SSI clock.

Best Regards,

Ralph Jacobi