Other Parts Discussed in Thread: TMS570LS0714, , HALCOGEN

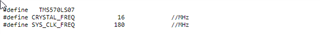

Hi, Im'm trying to compile a CAN bootloader for this microcontroller. Basically I saw on this forum someone sayig to use the example provided for TMS570LS0714, but actually, besides I was able to compile and flash it on the device, it seems like I can not get CAN comunication working.

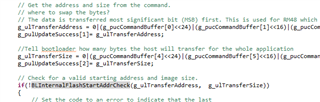

Basically whenever I try to send the "Download Command" message, the can buffer show "0x88,0x88,0x88,0x88,0x88,0x88,0x88,0x88, so g_ulTransferAddress and g_ulTransferSize are both 0x88888888888888.

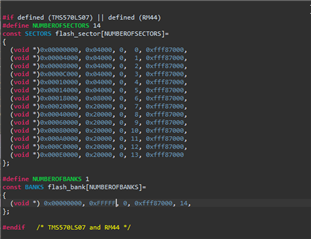

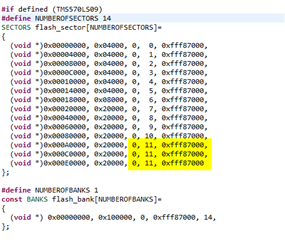

I'm not sure what I'm missing, I tried with RM46 launchpad and the example was working fine. I also defined the sectors as for the TMS570LS0914, so basically I'm not sure what I'm missing.

Does anyone have an example specific for this Microcontroller? Am I missing something? It is a bit upsetting the fact that there is documetatio for bootlaoder for this device an no source code from TI actually....

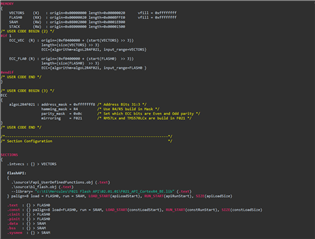

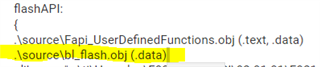

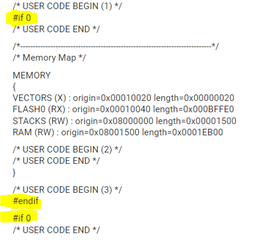

this is the bl_link.cmd file

this is the bl_link.cmd file

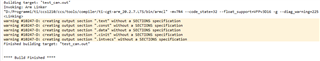

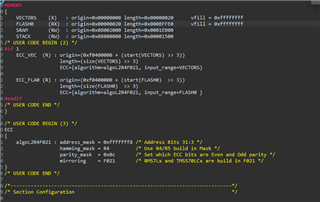

this is what i get when sending this fro PCAN Explorer

this is what i get when sending this fro PCAN Explorer