Other Parts Discussed in Thread: SYSCONFIG

Hi Expert,

I have a question regarding to the source of MCAN FCLK. In TRM spruj17b, MCAN FCLK can be one of XTALCLK, EXT_REFCLK, SYS_CLK, DPLL_PER_HSDIV0_CLKOUT1, DPLL_PER_HSDIV0_CLKOUT0, RCCLK10M, or XTALCLK.

However, if you look into MCAN loopback demos in AM263x MCU+ SDK8.03, the default parameter generated by syscfg is

#include "ti_drivers_config.h"

/*

* MCAN

*/

/* MCASP Default Bit timing Parameters */

MCAN_BitTimingParams gMcanBitTimingDefaultParams =

{

.nomRatePrescalar = 0x7U,

.nomTimeSeg1 = 0x5U,

.nomTimeSeg2 = 0x2U,

.nomSynchJumpWidth = 0x0U,

.dataRatePrescalar = 0x1U,

.dataTimeSeg1 = 0x3U,

.dataTimeSeg2 = 0x2U,

.dataSynchJumpWidth = 0x0U,

};

Base on these parameters, we can calculate MCAN FCLK

FCLK/BPR/(Sync + (Timeseg1+1) + (TimeSeg2+1))

The demo codes set 1M/5Mbps MCAN baud rate. so we can get FCLK = 80MHZ.

1 . But where is this 80MHz coming from????? Customer request we provide correct clock source description in TRM, can you please help?

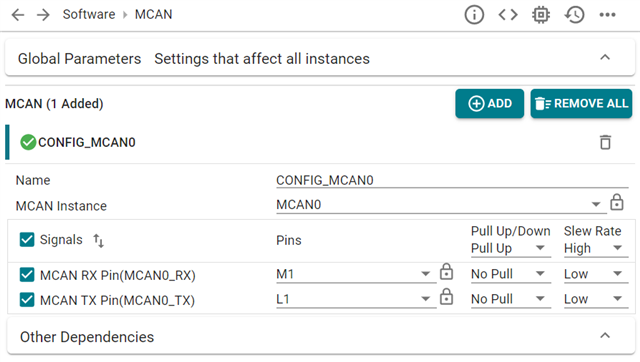

2. The syscfg doesn't provide clock source selection options.

Do we have plan the enable MCAN FCLK source selection option in next version of SDK?

Regards

Andre