Part Number: AM2634

Other Parts Discussed in Thread: SYSCONFIG

Hi,team

Here's the issue form the customer may need your help:

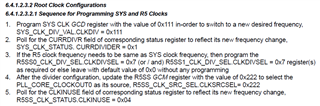

Using the ePWM module's routine to debug on the CC board, measure the PWM frequency and assume that the ePWM clock is 200 MHz, but the WUCPUCLK configured in sysconfig is 25 MHz, how does it multiply? It is seen in the chip manual that the clock for the AM263 is a few fixed frequency options such as 25MHz, 200MHz, 400MHz, etc., which is very different from the C2000 configuration PLL generation SYSCLK. SYSCLK is not described in the manual.

Could you help check this case?Thanks.

Best Regards,

Ben