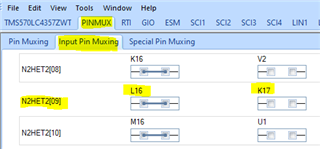

Part Number: TMS570LC4357

Other Parts Discussed in Thread: HALCOGEN

I've gone through the HET IDE tutorial and would like to implement a relatively simple clock generator.

From an externally generated 1 PPS clock, I'd like to generate a 5 msec 50% duty cycle period clock that is phase aligned (and hopefully "locked") to the 1 PPS one.

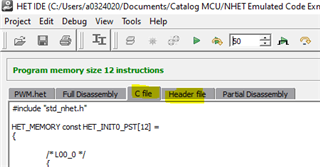

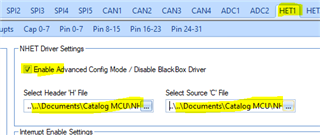

The Launchpad HET PWM project I've previously used produced a 5 msec clock (that generated periodic interrupts to the CPU) but it did not have any way to align to an external 1 PPS clock. And hence the use of the HET IDE is fitting. The microcode in HL_het.c in the HET PWM project seems to have more "meat" than I need, so I'm not sure "reverse engineering" it (is there any HET disassembler?) by the provided comments is that appropriate/useful.

Is there any HET IDE projects that could fast-track me to getting this done? I see some stuff in the algorithm library, include PWM projects, but they seem more fancy than anything I need.

I will try to gain more familiarity with the HET instructions and engine, but I'm not one for re-inventing the wheel if I can find a close-enough wheel to use as a start.

Thank you very much.