Other Parts Discussed in Thread: LP-AM243

Dear TI,

What is the proper way to configure HW to detect end of transmission?

Once the data are transmitted we want to switch to receiving mode or do some other operations.

It is important that we do not switch sooner.

We are using UART FIFO to buffer data to offload the CPU during TX operation.

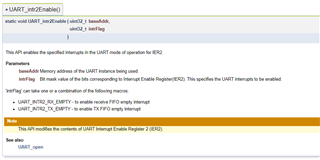

As soon as "Programmable FIFO threshold" level is hit and there are no more data to be put into UART_THR, the interrupt is disabled and transmission is done.

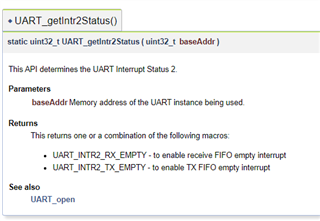

Starting at this point. Can we detect by interrupt "empty fifo buffer and shift register" to clearly indicate the time where all data are already transmitted?

UART_FCR: TX_FIFO_TRIG configuration do not seems to allow "0 spaces" option to be set.

0h = 8 spaces

1h = 16 spaces

2h = 32 spaces

3h = 56 spaces

It is unclean for me if it is even possible.

... p_serial_hw_hdl->p_params->readMode = UART_TRANSFER_MODE_CALLBACK; p_serial_hw_hdl->p_params->readReturnMode = UART_READ_RETURN_MODE_PARTIAL; p_serial_hw_hdl->p_params->writeMode = UART_TRANSFER_MODE_CALLBACK; p_serial_hw_hdl->p_params->readCallbackFxn = mbp_ti_uart_irq_rx_callback; p_serial_hw_hdl->p_params->writeCallbackFxn = mbp_ti_uart_irq_tx_callback; ... p_serial_hw_hdl->p_params->hwFlowControlThr = UART_RXTRIGLVL_56; // greater than or equal to the RX FIFO trigger level p_serial_hw_hdl->p_params->operMode = UART_OPER_MODE_13X; p_serial_hw_hdl->p_params->rxTrigLvl = UART_RXTRIGLVL_56; p_serial_hw_hdl->p_params->txTrigLvl = UART_TXTRIGLVL_56; ...

Thank you.

Best regards,

ms