Other Parts Discussed in Thread: SYSCONFIG

Dear all,

we need to use SPI in our project. To achieve this task, we imported the example project 'mcspi_loopback_am263x-cc_r5fss0-0_freertos_ti-arm-clang' first to test SPI controller.

We noticed a possible issue on the generated signal.

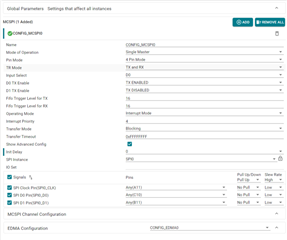

Attached you can find the example.syscfg pictures to show how the SPI is configured.

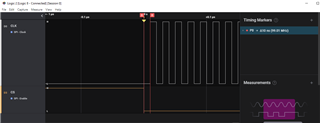

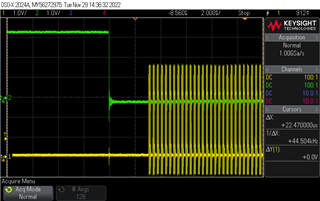

Below the picture with the captured signals (yellow is the CLK while green is the CS)

As you can see from configuration SPI frequency clock is 50 Mhz so we have a tclk = 20ns.

Since Chip select TCS is set to 0 it means 0.5 clock cycles delay; so we expect to have a delay of 10ns while we have a delay of 3us as you can see from the above picture.

Could you help us please?

Waiting for your kind reply

Thanks

BR

Gianni