Part Number: AM2434

Other Parts Discussed in Thread: LP-AM243, UNIFLASH

Hi Team,

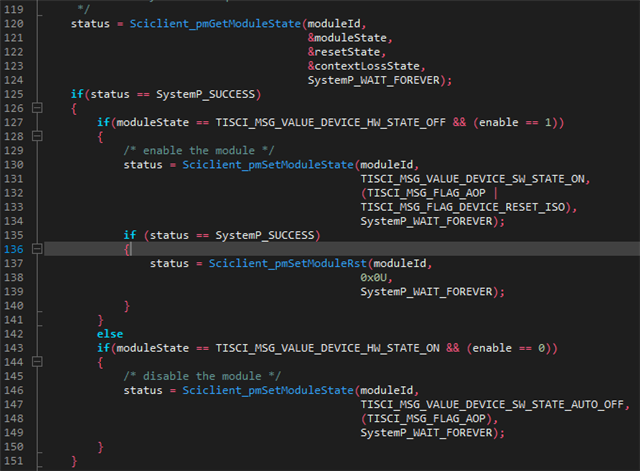

When I was debugging the board, I found that the PowerClock_init() function wasn't working well. I traced it and found that it was because of the CUR_CNT of the DMASS0_SEC_PROXY_0_STATUS register of DMASS0. After the message was sent by Sciclient_sendMessage(), CUR_CNT could not set the count as 1.

Could you please tell me, when Sciclient_sendMessage() sends a message, on what conditions can the CUR_CNT of the DMASS0_SEC_PROXY_0_STATUS register of DMASS0 receive the count and set it as 1? How should DMASS0 be set?

Best regards,

Katherine