Other Parts Discussed in Thread: SYSCONFIG

HI,

Without SYSPLL enabled, every download will succeed. After downloading the firmware that used SYSPLL as the clock source for MCLK, each download failed for the first time and needed to be downloaded again within a few seconds to succeed. This problem exists whether the clock source of SYSPLL is SYSOSC or HFCLK. The development environment is keil + jlink + swd. The connection signals are VCC, GNDS, SWDIO, and SWCLK. keil prompts a ‘Flash Timeout, Reset the Target and try it again’ on failure. What is the cause of download failure and how to solve it?

The following configuration has this problem:

SYSCTL.useHFCLK_Manual = true;

SYSCTL.HFCLKSource = "HFXT";

SYSCTL.HFCLK_Freq = 16000000;

SYSCTL.HFXTStartup = 10;

SYSCTL.HFCLKMonitor = true;

SYSCTL.EXCLKSource = "SYSPLLOUT1";

SYSCTL.HSCLKSource = "SYSPLLCLK2X";

SYSCTL.SYSPLLSource = "HFCLK";

SYSCTL.SYSPLL_CLK2XEn = true;

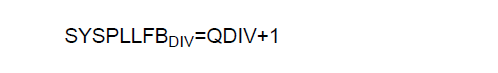

SYSCTL.SYSPLL_Qdiv = 5;

SYSCTL.MCLKSource = "HSCLK";

SYSCTL.SYSPLL_Pdiv = 2;

SYSCTL.UDIV = "2";

Best regards,

Jason