Other Parts Discussed in Thread: SYSCONFIG, AM2732

Hi TI experts,

I'm trying to connect the Sitara eval module to an our custom board with CSI IF.

In order to check the connection, I'm using the CSI-RX examples under the mcu plus sdk version 08.04.00.17.

As written in the SDK, this example is not working with an external CSI2 device but it's working only internally.

We modified the example code to work with the custom board but it's not working.

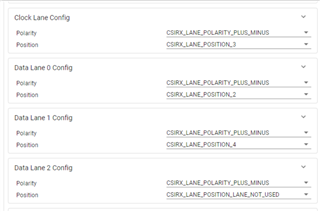

The CSI on the custom board has this parameters:

- 2 data lanes (D0 and D1)

- 1 CLK lane with freq of 160MHz (320Mbps each lane).

- the CSI IF is connected to the connector J1 of the Front end 1.

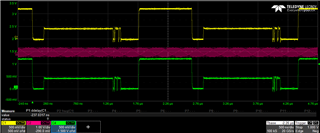

I've checked the CSI with oscilloscope and it runs as expected.

Regarding the code these are the steps made:

1) Import the example with CCS Version: 11.2.0.00007

2) commented the part of "CSIRX_debugModeGenerateFrames" and "CSIRX_debugModeEnable"

3) changed the configuration with sysvconfig to match the HW

4) added two more interrupts for the Line Start Detect and Frame Start Detect.

With this code no interrupts was generated even if the CSI is running.

What I should check in the firmware to debug the problem?

In which document I can find the correspondence between the Data Lane Config Position of the sysconfig and the real pin of the device?

Thanks.