Hello,

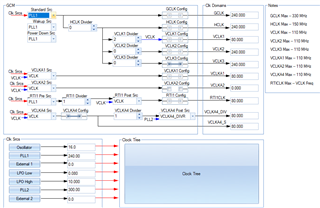

I am facing a problem where the HET is not Initializing after a Power on Reset. This does not happen after every POR but happens quite often.

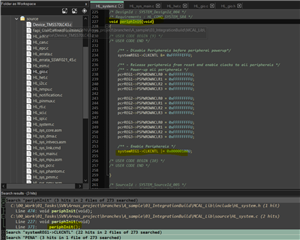

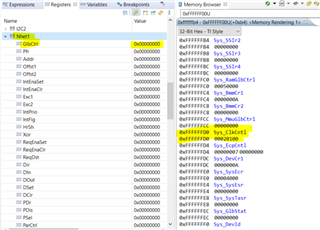

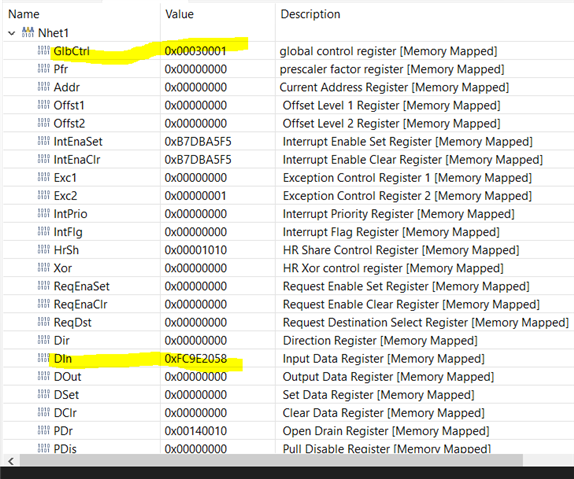

The below Picture is in case of normal HET Initialization where HET Hardware is ON and Data can be seen in the DIN Register.

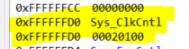

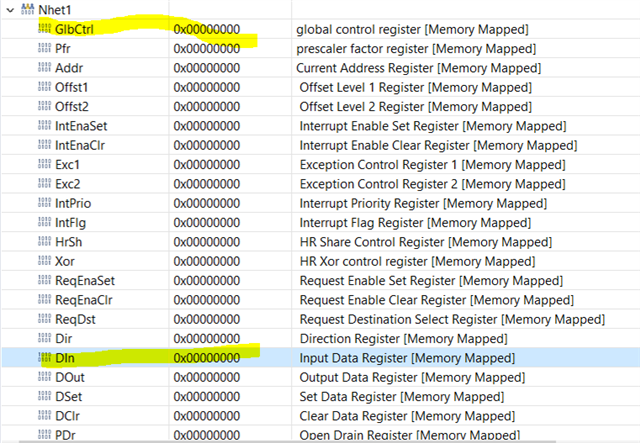

The below Picture is in case of abnormal HET Initialization where HET Hardware is OFF and Data cannot be seen in the DIN Register. We can recover from this Problem by doing a POR.

Can you please assist me in this Issue.

Kind Regards,

Sakti