Part Number: LP-AM243

Hi Champs,

I am asking for my customer here.

For ICSS_G0, we have one TX_FIFO Per MII? Right? Like the ICSS_G0 has two MII, so two TX_FIFO? Thanks.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Part Number: LP-AM243

Hi Champs,

I am asking for my customer here.

For ICSS_G0, we have one TX_FIFO Per MII? Right? Like the ICSS_G0 has two MII, so two TX_FIFO? Thanks.

Hello Shaoxing,

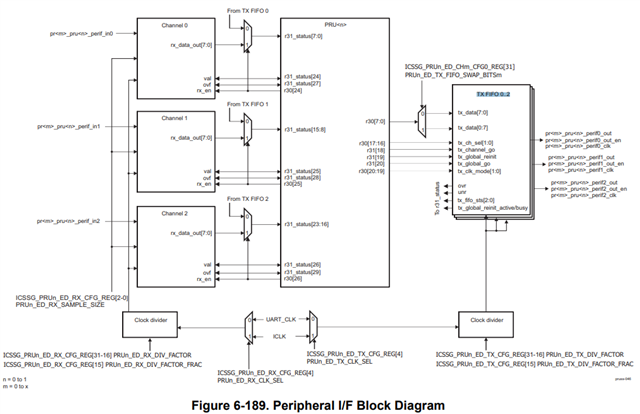

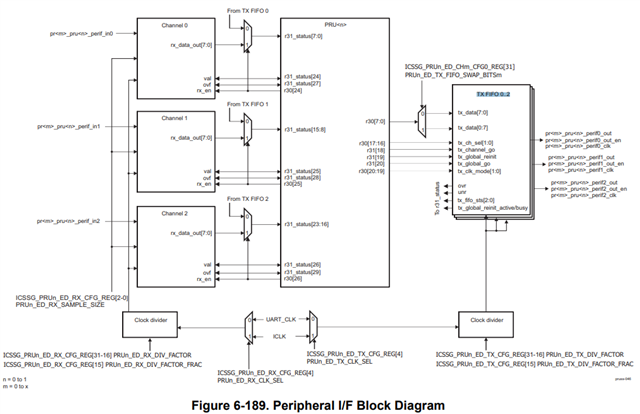

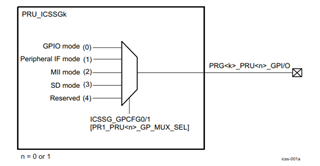

The graphic shown above is in relation to the ICSSG being used in the Peripheral mode to support encoder protocol such as EnDat 2.2. MII mode and PERIF mode cannot be used at the same time for a singular PRU core of the ICSSG. Each PRU core's I/O mode is determined by the PRG<n>_PRU<n>_GP_MUX_SEL register.

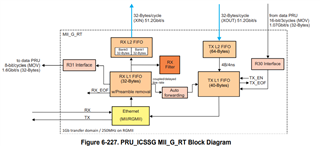

Each ICSSG has two PRU cores and each PRU core can be in MII mode. So there are two possible MII ports per ICSSG and each MII port has 40-Bytes TX L1 FIFO and 64-Bytes TX L2 FIFO.

For more information about the ICSSG in MII mode, refer to Chapter 6.4.11 of the AM243x TRM.

Regards,

Erik