Hi,

We have our own design for the power supply reset of the controller (TMS570LS0432). We want to delay the reset of the controller when the VCCIO supply is not in the acceptable range. However, we have an additional chip that is capable of detecting the VCCIO under voltage and Over voltage conditions. And, the SW will then control the nPORRST pin.

We need the following information.

1. The core runs on VCC supply (1.2V). (Same is true for RAM and FLASH memories. They all have VCC supply). Now, the question is, if the VCCIO supply is not in the acceptable range, Can the code execution be trusted?

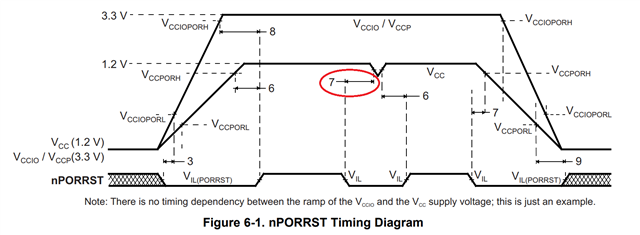

2. Are there any consequences if we do not take care of the power-down sequence of the VCCIO supply with regard to the datasheet? Please see the section "6.2 Power Sequencing and Power-On Reset" of the data sheet.

Looking forward to hearing from you. Many thanks in advance,

Best regards,

Sreekanth Challa