Hi experts,

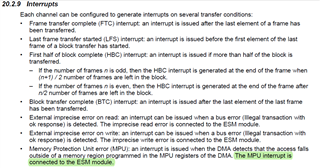

During the implementation of the DMA9A Diagnostic mentioned in the Safety Manual, we noticed that ESM 1.2 does not get set on the forced memory access violation of the dma.

However the REG0FT bit gets set (we are testing region0).

Based on this, the test seems to work as intended, but signalling the error to esm seems to be disabled.

But we noticed that ESM 1.2 Error is set, when INT0ENA is set. As far as we understand, this bit enables all interrupts of the dma module region 0.

(Q1) Is the signalling of the ESM error dependend on the enable state of all dma-interrupts?

(Q2) If this is the case, how can we enable ESM error signalling without using the dma Interrupts FTC, LFS, HBC, and BTC ?

Thank you and best regards,

Max