Part Number: AM2434

Hi Team,

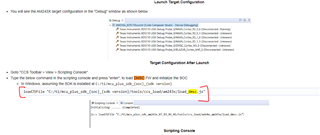

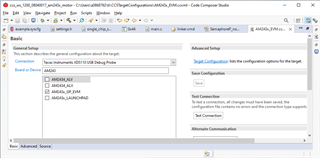

While implementing "fsi_loopback_polling_am2434-evm_r5fss" example, i am getting following error.

My booting selection is "11011110" for BOOT0-7 & "01000000" for BOOT8-15.

I haven't loaded any firmware in any RAM or SD card, just implementing above example using XDS110 debugger.

Please help me out, why I am getting above error.

Waiting for your feedback.

--

Thanks & Regards,

Divyesh Patel