Other Parts Discussed in Thread: HALCOGEN

Hi,

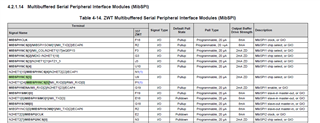

I'm starting out with a TMS570LC4357 design and will be using many SPI interfaces and devices that I can't daisy chain, hence I will require separate chip selects to each device.

I just want to get something 100% clear in my mind upfront before progressing regarding the multiplexed pins.

For example Pin R2 - MIBSPI1NCS[0]/MIBSPI1SOMI[1]/MII_TXD[2]/ECAP6

Can you confirm that if I am using MIBSPI1 as a 2 bit interface i.e. MIBSPI1SOMI[1:0], that I will only be able to utilise the MIBSPI1NCS[4:1] pins?

i.e. MIBSPI1NCS[0] is inaccessible as it is now configured for use in the 2 bit data transfer.

Likewise if I utilise the all the N2HET1's pins (F3, G3 & J3) then I can only use the MIBSPI1NCS[4] output us a chip select.

So looking through the various mux'd pins it looks like using a selection of peripherals may mean that other peripherals, or parts of their functionality, will not available to me. Which is when the real development fun starts :)

If I am correct in all the above, is there a tool maybe in Excel that will show me what is available if certain pins are allocated? I am guessing HALCoGen may do this, but I've not delved into this yet as I'm looking from a hardware allocation side of things.

Regards

John