Other Parts Discussed in Thread: HALCOGEN

Hi,

I am developing a code where DMA is used for receiving transactions arriving to the SCI peripheral.

The program normally works during a couple of minutes but in the end it gets stuck.

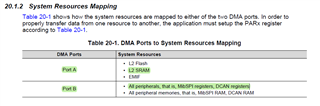

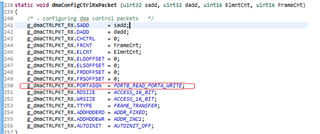

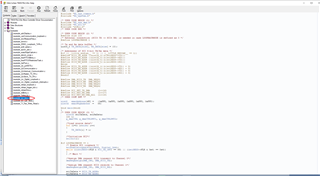

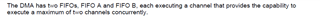

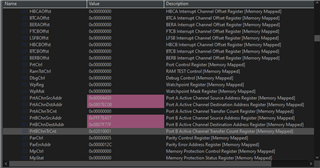

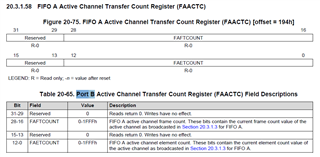

Debugging It, it is observed that when this occurs the FIFO (sometimes called port in the spnu563a and in CCS) has changed from A to B. (During nominal operation portb registers in pink, including trfcount, is at 0s)

From my understanding the program does not make that FIFO change, moreover I don't know if it is possible to do that somehow.

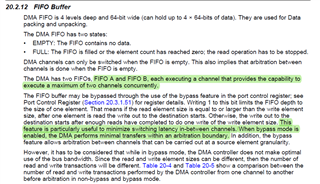

Also, there is a bit of mixing in the naming convention for those registers as in CCS appear as in the image above but in the spu563 are referred more as FIFO than as PORT although sometimes are mixed those words too.

I don't know if there could be an explanation for this behaviour, that is for changing from PORT/FIFO A to B automatically or if there is a way to avoid it or there is a way to make it back to FIFO/PORT A.

Many thanks in advance and regards.