Hello,

I am trying to read multiple 16bit words over SPI from an external ADC.

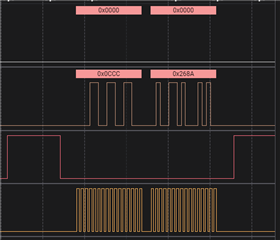

I can see the frames I need on a logic analyzer but when I read the MCSPI_RX register I keep getting just the first word multiple times instead of the remaining elements in the RX FIFO.

This is my code:

/* SPIEN line is forced to low state.*/

MCSPI_writeChConfReg(baseAddr, chNum, gCsAssertRegVal);

while(transferLength!=0)

{

/* Write Effective RX FIFO depth */

if (transferLength >= effRxFifoDepth)

{

transferLength = effRxFifoDepth;

}

while (0 == (MCSPI_readChStatusReg(baseAddr, chNum) &

CSL_MCSPI_CH0STAT_TXFFE_MASK))

{

/* Wait for Tx FIFO to be empty before writing the data. */

}

/*Loops for retrieving the multiple SPI words*/

for(uint8_t i=0;i<transferLength;i++) //transferLength for this example is 2 (bytes)

{

MCSPI_writeTxDataReg(baseAddr, 0x00000000, chNum); //writing dummy TX data

}

for(uint8_t i=0;i<transferLength;i++)

{

rxBuff[i]=(uint16_t)MCSPI_readRxDataReg(baseAddr, chNum); //rxBuff points to Rxbuffer_16

if(en_Chn_Seq_Idx[i]!=0xAA) //writing relevant data into shared memory

{

shmem.ADC_Buff[en_Chn_Seq_Idx[i]][db_idx][curr_dbuf_dpt]=rxBuff[i]; //write data into shm.mem double buffer

}

}

numWordsRead += transferLength;

transferLength = length - numWordsRead;

}

while (0 == (MCSPI_readChStatusReg(baseAddr, chNum) &

CSL_MCSPI_CH0STAT_TXFFE_MASK))

{

//Wait for Tx FIFO to be empty for the last set of data.

}

while (0 == (MCSPI_readChStatusReg(baseAddr, chNum) &

CSL_MCSPI_CH0STAT_EOT_MASK))

{

/* wait for the end of transfer of last word.*/

}

/* Force SPIEN line to the inactive state.*/

MCSPI_writeChConfReg(baseAddr, chNum, gCsDeAssertRegVal);

I used the mcspi performance 32bit example code as a reference for my code.

And the configuration I am using is :

I also noticed that when I go through the code line by line in debug mode, I see the MCSPI_RX register getting updated as it should after each MCSPI_readRxDataReg() function call.

So, I assumed I might not be giving enough time for the MCSPI_RX buffer to be updated with the next element from the FIFO after reading it.

So I tried the below code:

for(uint8_t i=0;i<transferLength;i++)

{

MCSPI_writeTxDataReg(baseAddr, 0x00000000, chNum);

while(0 == (MCSPI_readChStatusReg(baseAddr, chNum) &

CSL_MCSPI_CH1STAT_RXS_FULL))

{

/*wait till element is read into the fifo*/

}

rxBuff[i]=(uint16_t)MCSPI_readRxDataReg(baseAddr, chNum);

if(en_Chn_Seq_Idx[i]!=0xAA) //writing relevant data into shared memory

{

shmem.ADC_Buff[en_Chn_Seq_Idx[i]][db_idx][curr_dbuf_dpt]=rxBuff[i]; //write data into shm.mem double buffer

}

}

The difference being, Instead of reading the MCSPI_RX register in a loop, I wait for RXS bit of the MCSPI Status register to be FULL before reading the MCSPI_RX register for the next word.

This seems to work, but it introduces additional delay between two words which is undesirable.

Is there anyway to read MCSPI_RX register without having to wait for any status bits?

Am I approaching this issue the right way?

Thanks and Regards.