Other Parts Discussed in Thread: SYSCONFIG

Hello Champs,

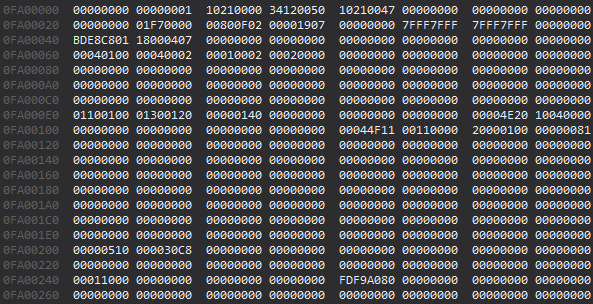

In R5 code, customer enabled both PRU and MMC interrupts. The priority of PRU is higher than MMC's. In PRU ISR function, it communicates to MMC. The interrupt status bit in MMCSD1_NORMAL_INTR_STS(Normal Interrupt Status Register,0FA0 0030h)and MMCSD1_ERROR_INTR_STS(Error Interrupt Status Register,0FA0 0032h) registers are not set.

Customer enabled all the interrupt.

Why the mmc interrupt can't be set in PRU interrupt?

Thanks

Regards

Shine