My design connects a Lattice XO3LF_6900C FPGA I2C interface to the AM2432.

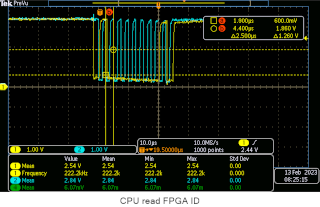

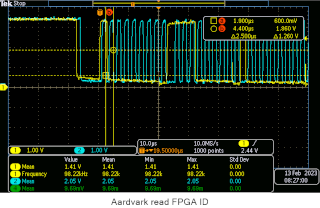

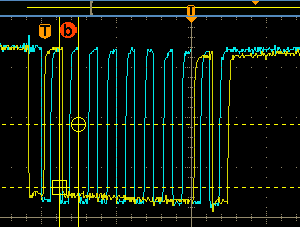

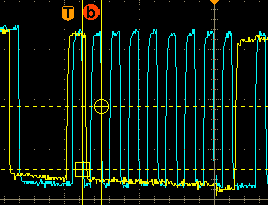

The FPGA does not acknowledge the I2C address when using the I2C configuration and driver from MCU_PLUS_SDK_AM243x_08_05_00_24. However with an Aardvark device, I do get proper access. The difference is a delay after the start condition (see pictures below).

Is there any way to configure such delay?