Part Number: MSP432-DEBUGGERS

I am trying to implement an I2C Read function to support the KT0806L_V1.8 FM Modulator device which requires a repeated start condition in my MSP432 project:

I am running the Bluetopia Stack v4.2.1.1. The write works fine, however when trying to do a read that has a repeated start condition I run into problems because the peripheral wants to send a stop condition after the write command is sent with the address value of where the read is suppose to happen from. This causes the sequence to end and the read return invalid data.

I have read many threads and I have seen how you must trick the peripheral inside of the TX Isr by switching modes to Receive before the last byte goes out, etc. This is how the sample driver library(below) tries to do it but that does not work for me with the default sample project:

C:\temp\msp432_driverlib_3_21_00_05\msp432_driverlib_3_21_00_05\examples\MSP432P4xx\i2c\i2c_master_rw_repeated_start-master_code.

I was able to get the following code supplied by a user on this forum to work in a stand alone sample project:

However, when I port this to my A3DPDemo_Src project it does not work. The stop condition is generated by the peripheral and kills the repeat start condition thus breaking the read function all together and causing the state machine on the KT Micro device to return incorrect data for the read.

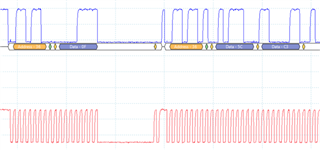

This is a good read using the sample code I got from the link above. You can see the stop condition happens and the read brings back a valid value.

And when adding the same code in my Project you can see that the stop condition happens and read returns bad data:

Furthermore, the sequence never ends leaving the peripheral in an unknown state.

Since I noticed that the I2C peripheral is very timing dependent I would like to add that the sample code is running at 3MHz MCLK speed and baud rate of 100Kbps while my Project has a 24Mhz clock and 100Kbps baud rate. I essentially tried to increase the delays in the code by 8X but that did not work.

This is the code I am using for both the sample project and the project I am developing on.

//Turn on FM Mod

GPIO_setOutputHighOnPin(GPIO_PORT_P4, GPIO_PIN6);

//GPIO_setOutputHighOnPin(HRDWCFG_FM_EN_PORT_NUM, HRDWCFG_FM_EN_PIN_NUM);

GPIO_setAsOutputPin(GPIO_PORT_P4, GPIO_PIN6);

/* Disabling the Watchdog */

MAP_WDT_A_holdTimer();

/* Select Port 1 for I2C - Set Pin 6, 7 to input Primary Module Function,

* (UCB0SIMO/UCB0SDA, UCB0SOMI/UCB0SCL).

*/

MAP_GPIO_setAsPeripheralModuleFunctionInputPin(GPIO_PORT_P1,

GPIO_PIN6 + GPIO_PIN7, GPIO_PRIMARY_MODULE_FUNCTION);

/* Initializing I2C Master to SMCLK at 400kbs with no autostop */

MAP_I2C_initMaster(EUSCI_B0_BASE, &i2cConfig);

/* Specify slave address */

MAP_I2C_setSlaveAddress(EUSCI_B0_BASE, SLAVE_ADDRESS);

/* Set Master in transmit mode */

//MAP_I2C_setMode(EUSCI_B0_BASE, EUSCI_B_I2C_TRANSMIT_MODE);

/* Enable I2C Module to start operations */

MAP_I2C_enableModule(EUSCI_B0_BASE);

__delay_cycles(10000);

/* Send out start + address + 1 data byte */

MAP_I2C_masterSendMultiByteStart(EUSCI_B0_BASE, TXData);

//wait for first byte to be moved to shift register

while(!(EUSCI_B0->IFG & EUSCI_B_IFG_TXIFG));

EUSCI_B0->IFG &= ~(EUSCI_B_IFG_TXIFG);

// Before the restart is sent, app has to wait for current TX byte + ack to complete

// This takes 9 cycles at 100kHz = 90uS

// The MCLK default = ~3MHz

// to complete the 1 byte TX app needs to wait ~270 MCLK cycles at a minimum

__delay_cycles(300);

//clear the TR bit to setup master as receiver

EUSCI_B0->CTLW0 &= ~(EUSCI_B_CTLW0_TR);

// Send the start + address

EUSCI_B0->CTLW0 |= EUSCI_B_CTLW0_TXSTT;

// wait for address to be sent

while(!(EUSCI_B0->CTLW0 & EUSCI_B_CTLW0_TXSTT));

// set stop immediately to ensure only one byte is read

EUSCI_B0->CTLW0 |= EUSCI_B_CTLW0_TXSTP;

// poll RX flag

while(!(EUSCI_B0->IFG & EUSCI_B_IFG_RXIFG0));

// Read from Receive buffer

RXData = EUSCI_B0->RXBUF;

// ensure I2C transaction has completed

while (MAP_I2C_masterIsStopSent(EUSCI_B0_BASE));

Thanks in advance for helping me out with this issue.