Dear Champs,

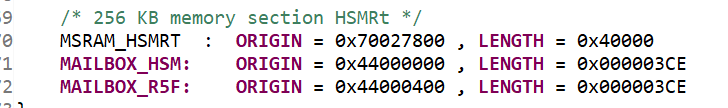

My customer found HSMRT memory region in sbl_qspi example of MCU+SDK v8.5.0.24 as below, and want to know how this memory region can be moved or if this region can be overlayed after loading.

1. Could you please let me know how MSRAM_HSMRT memory region can be moved to other region?

2. Could you please let me know if this memory region can be overlayed with other memory after downloading FW to HSM internal memory?

Thanks and Best Regards,

SI.