Other Parts Discussed in Thread: AM2434

I am trying to set a breakpoint on R5FSS1-0 core on a AM2432

I have CCS 12.2.0.00009, SDK mcu_plus_sdk_am243x_08_05_00_24, syscfg 15.0, compiler CLANG 2.1.2

If I don't set any breakpoint the firmware run normally

If I start debugging from main step by step, no issues.

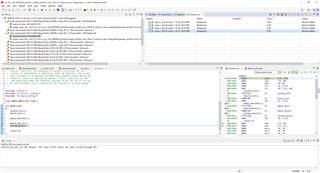

But as soon as I set a breakpoint I get this message:

Here is my map file: canopen.Debug.map

Here is the binary .out: canopen_am243x-titan-prod_r5fss1-0_nortos_ti-arm-clang.out

Looking forward

Andrea