Other Parts Discussed in Thread: SYSCONFIG

Hi experts,

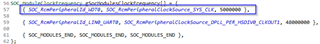

Sysconfig generates the configuration code for WDT and clk. For WDT, by default, it uses the SYS_CLK as clock source and the final clock frequency is set as 5M as following shown:

So that means the clk divider value should be 40.

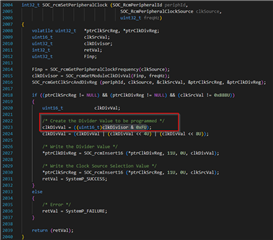

However in API of SOC_rcmSetPeripheralClock, I found that the actual divider value will be equal to expected divider value & 0xF as following:

So the actual divider value will not 39 (40-1) but 7, which means the actual clk frequency of WDT will be 25M but not 5M.

Please check it and give your comments. Thanks.

Thanks,

Will