Other Parts Discussed in Thread: AM2634, AM2434

Dear Champs,

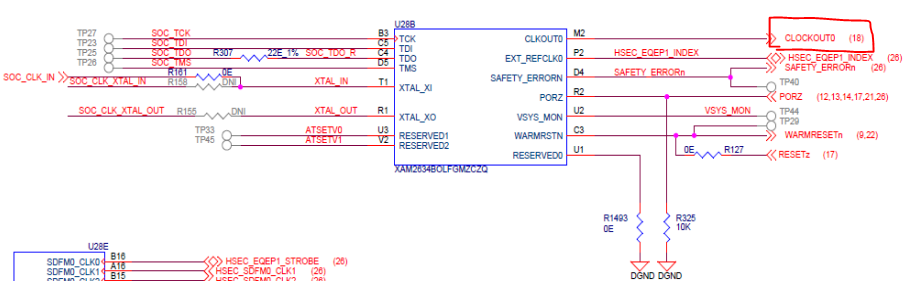

Is it possible to output 50Mhz Clock through CLKOUT0 pin of AM2634 in below?

If so, how it can be changed?

Thanks and Best Regards,

SI.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hello Sung-IL,

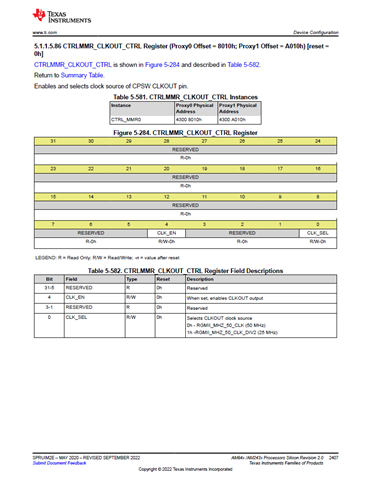

The CLOCKOUT0 pin has a dedicated CTRLMMR_CLKOUT_CTRL register as described in the device TRM (AM243x TRM (Rev. E). Including screenshot below for reference.

To enable 50 MHz signal, Bit0 (CLK_SEL) should be set to 0, and Bit4 (CLK_EN) should be set to 1.

Best Regards,

Zackary Fleenor

Hi Zackary Fleenor,

Thanks for the response.

I'm questioned about AM2634, not AM2434. I could find CTRLMMR_CLKOUT_CTRL in AM2634 TRM, but could not find CTRLMMR_CLKOUT_CTRL in AM2634 register TRM.

And also, as I understand, the default CLK_OUT is 25Mhz, How it can be set to 50Mhz?

Thanks and Best Regards,

SI.

Hello,

Apologies for the device mix-up here.

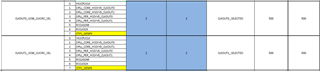

For, AM263x the default clock source for CLKOUT0 is CORE_PLL_HSDIV0_CLKOUT1 by default (500 MHz).

You could then configure the TOPRCM_CLKOUT0_DIV_VAL to AAAh (multi-bit decimal 10), this divider will result in 500/10 = 50 MHz signal provided to the CLKOUT0 pin.

Best Regards,

Zackary Fleenor