Hello,

we have a problem currently with the Ethernet-Phy DP83826 and the startup behavoir with PRU for a profinet application.

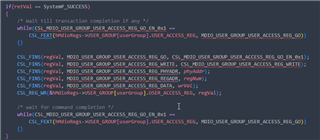

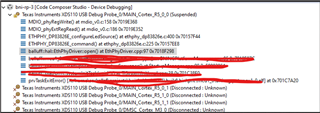

In some cirumstances It could happend that your system at boottime hangs. Call-Stack looks like this:

After investigation and having a look again at the datasheet we supsect the following:

this is the timing diagram from the datasheet of the phy (https://www.ti.com/lit/ds/symlink/dp83826e.pdf?ts=1678218095288&ref_url=https%253A%252F%252Fwww.ti.com%252Fproduct%252FDP83826E%253Futm_source%253Dgoogle%2526utm_medium%253Dcpc%2526utm_campaign%253Dasc-hsdc-null-prodfolderdynamic-cpc-pf-google-wwe_int%2526utm_content%253Dprodfolddynamic%2526ds_k%253DDYNAMIC%2BSEARCH%2BADS%2526DCM%253Dyes%2526gclid%253DCjwKCAiA3pugBhAwEiwAWFzwdb4sYbCQUZV18rs1rh86aH9xVML3ynoSHK56YaMTRXRG9s2IZcm8xRoC2QYQAvD_BwE%2526gclsrc%253Daw.ds)

T4 is defined to a maximum of 50 ms which means that we need to wait this time after reset release to be sure the Eth-Phy is booted completly.

Here are my questions about this:

It seems to be that we are not waiting long enough and sending the command to early. This brings the hole system into a non-responsive state, where it just idles in the above call-stack.

Shouldn't this 50ms be handled at the PRU level? Atleast we should get on application level an error code which indicates something like: "PRU not ready" or/ and "EHTPHY not ready"

I think the reset Pin of the ETH-Phy is also driven by PRU so this should be handled by the SDK.

Is there already a function to check if PRU and ETH-Phy is booted completly?

But atleast I think the "command-function" of the ETH-Phy driver should return a error code as mentioned before.

Thanks

Fabian