Other Parts Discussed in Thread: HALCOGEN,

Explain the detailed process to enable 256 BUFFERS/EXTENDED_BUF_ENA Feature OF MibSPI.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Explain the detailed process to enable 256 BUFFERS/EXTENDED_BUF_ENA Feature OF MibSPI.

Hi,

By default, MibSPI supports up to 128 buffers for both Tx and Rx. Refer device specific datasheet if 256 buffer extension is implemented for the specific MibSPI instance in the device. If specific MibSPI instance supports 256 buffer extension, then follow below steps to enable it.

HALCoGen modifications are sufficient till 128 buffers but to work with more than 128 buffers it is required to do some manual modifications in the code along with HALCoGen configurations.

Example configuration for 256 buffers in MibSPI1 for TMS570LC4357

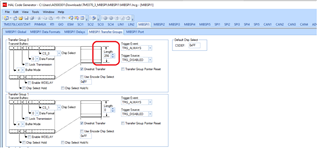

1. Configure buffer length as 256 in HALCoGen for MibsSPI1

2. Write 0xA to EXTENDED_BUF_ENA bit field of MIBSPIE register:

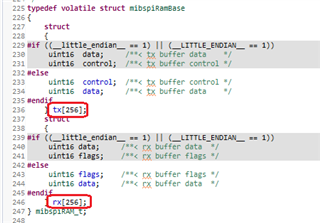

3. HL_reg_mibspi.h

change tx[128]/rx[128] to tx[256]/rx[256] of mibspiRAM_t struct

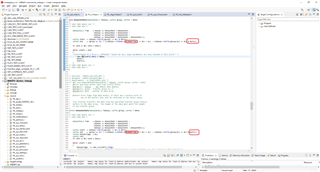

4. HL_mibspi.c

change 0x00007F00U to 0x0000FF00U,

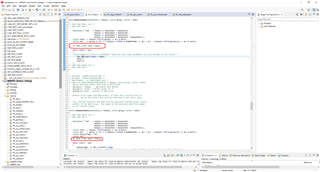

5. HL_mibspi.c

change if (end == 0U) {end = 126U;} to the if (end == 0U) {end = 256U;}

And below is the example project you can refer for above modifications.

In above project i enabled digital loopback and i transmitted 256 values using TG0 Extended buffer of 256 and i received same to the receiver buffer.

And similarly, you can configure required number of buffers from 129 to the 256 in buffer length field for Extended buffer mode like as shown in step 1 and do the remaining modifications as it is.

--

Thanks,

Jagadish.