Other Parts Discussed in Thread: HALCOGEN, TMS570LC4357

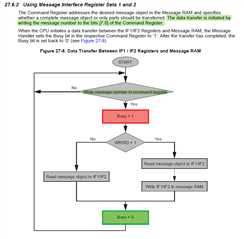

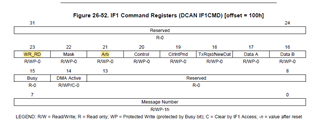

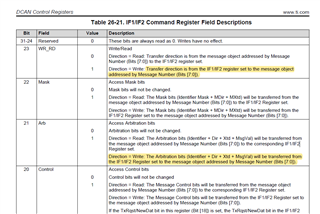

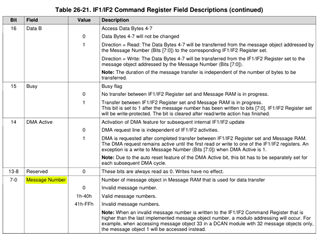

I'm trying to understand the IF2CMD register; more specifically the Message Number Field.

I do not understand where to find how to decode the value in this field in the documentation.

For example, to initialize a message box, HalCoGen use:

canREG2->IF2CMD = (uint8) 0xF8U;

To update ID, HalCoGen use

node->IF2CMD = 0xA0U;

What's the full description of those bits?

How can I configure the If2CMD register to modify the IF2ARB bits to enable ISR?

Regards,

Gabriel