Other Parts Discussed in Thread: ADS7038-Q1, ADS7038

Hi,

based on the on-going thread:

I tried to relax the DMA sequence requests from 1.25us downto 5us. To do so I did want the EDMA to burst write 4 Channel requests for the external SPI-ADC into the FIFO of the MCSPI on-chip component. However doing so, the SPI-TX direction 'dies out' after a few transfers. The EDMA3 is configured to use ABSYNC mode to do so. I read in the chip errata (i2350) that there seems to be an issue with this DMA mode with respect to MCSPI on-chip IP's. However I do not really understand the meaning of the description. I tried to use the work around. However nothing better happened. Therefore I assume I do get something wrong. Any hint on how to use the workaround for the EDMA + Fifo mode in my example within the MCSPI would be appreciated.

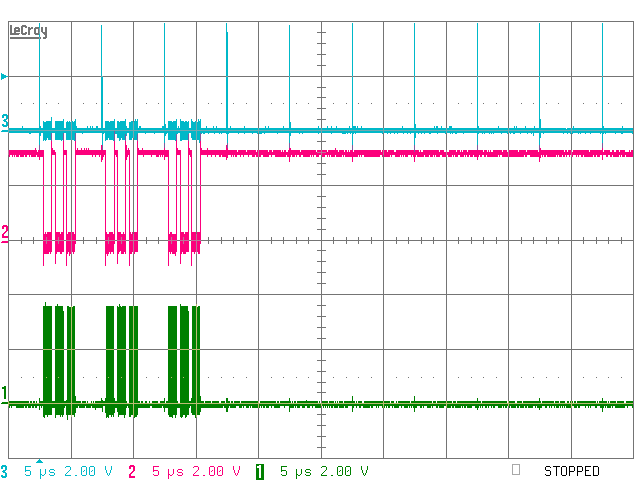

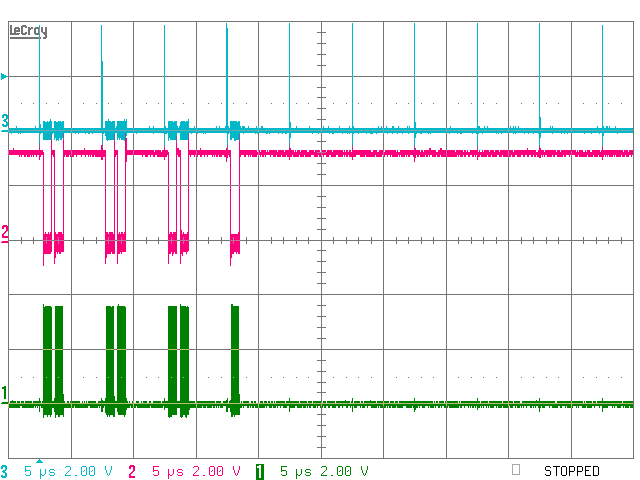

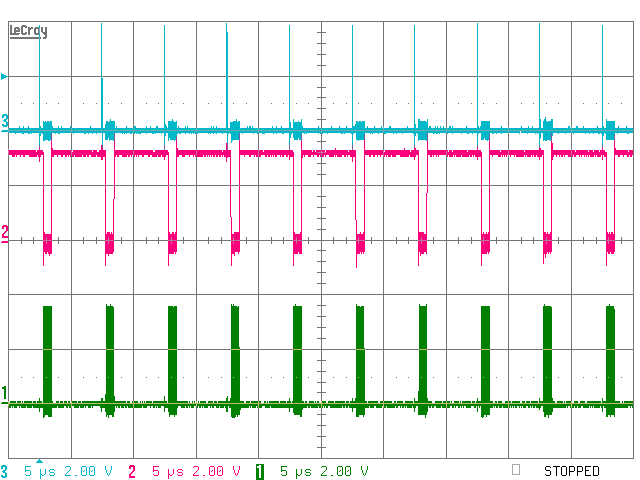

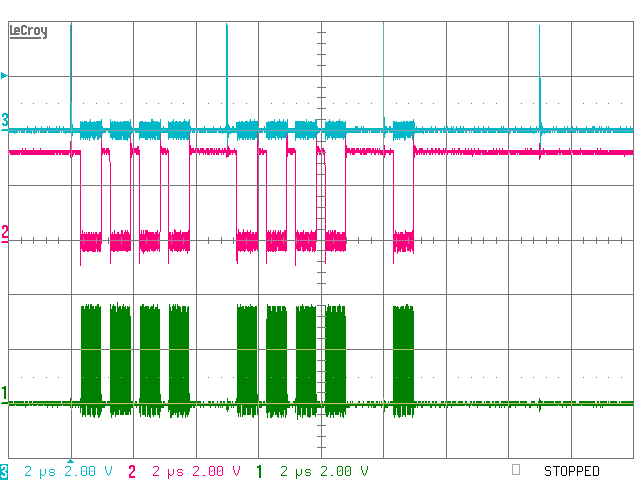

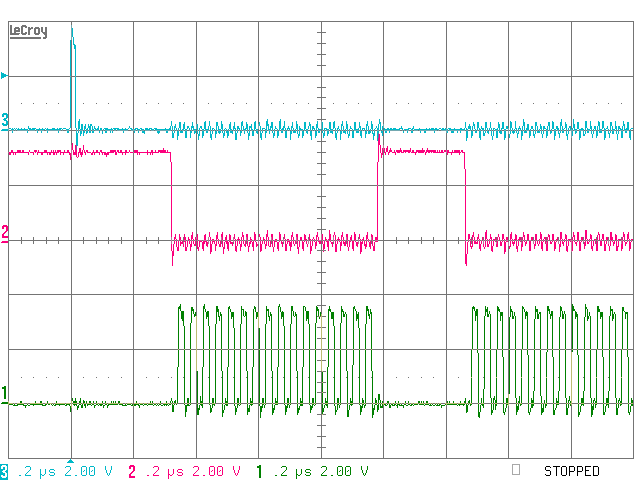

Legend:

- Ch3 (Blue) : EDMA trigger every 5 us

- Ch2 (Magenta): MCSPI SPI-CSn output. It runs at max speed with respect to the SPI-Clk

- Ch1 (Green) : MCSPI SPI-Clk. SPI-Clk frequency is 25 MHz.

Two 5us SPI burst sequences do work. Then it dies out. No more SPI-Tx activitiy. Root cause not known. The EDMA trigger still occurs every 5 us (Blue-Trace). The EDMA3 is configured to run endless on this channel.

Same scope-shot as the first one. However zoomed in. In this setup the SPI-CSn (Magenta trace) does not meet all the requirements for the ADS7038-Q1 with respect to the chip select period time which is > 1us. ADS7038 SPI-CSn high time > 230ns, low time > 400ns are met. ADC sampling period is violated a small amount. However lowering the SPI-Clk frequency may(!) result in a combination that would work and may fullfil all the timing requirements.

I did configure the EDMA channel for transmission to write 4 words (16Bit words) into the Fifo of the MCSPI. This shall happen every 5 usec. It does start up as expected. However after two sequence it dies out. Does this relates to what has been described in the chip errata (i2350)?

br

Markus