Hi,

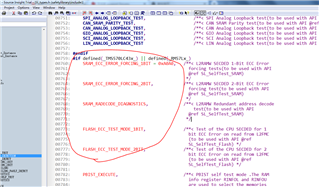

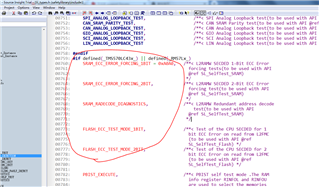

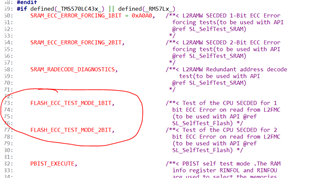

After carefully reading the diagnostic library code, I didn't find that SRAM/FALSH have fault injection test types for RM57Lx device.

Can you help check it please? If really not, how to perform fault injection for them?

Thanks.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi,

After carefully reading the diagnostic library code, I didn't find that SRAM/FALSH have fault injection test types for RM57Lx device.

Can you help check it please? If really not, how to perform fault injection for them?

Thanks.

Hi QJ,

But you don't give the answer on how to inject fault for RM57Lx SRAM/FLASH test.

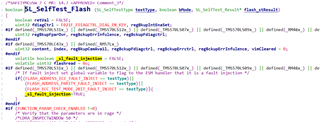

We can't set "_sl_fault_injection=TRUE" for RM57Lx device.

_sl_fault_injection is set only when the test type is fault injection. We use the same way for Flash ECC selftest and Flash ECC error fault injection. The fault injection test doesn't apply to TMS570LC43x and RM57x.

I dont' understand exactly the meaning of "We use the same way for Flash ECC selftest and Flash ECC error fault injection".

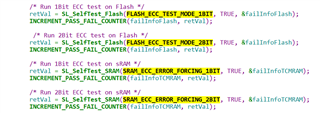

For RM57Lx, it just support test type "FLASH_ECC_TEST_MODE_1BIT/FLASH_ECC_TEST_MODE_2BIT".

It seems we can just do selftest for RM57Lx Flash ECC. How to do fault injection for RM57Lx flash ECC error?

Hi,

The fault injection is to inject faults into hardware logic and examine the effects. The FLASH_ECC_TEST_MODE_1BIT and the FLASH_ECC_TEST_MODE_2BIT are diagnostic tests with 1-bit or 2-bit ECC error injected to ECC logic.

Hi QJ,

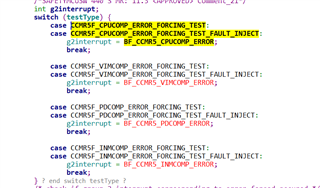

Not just SRAM/Flash, CCMR5F module has the same problem.

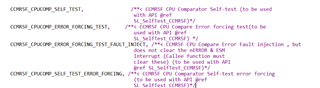

What's the exact difference between XXX_ERROR_FORCING_TEST and XXX_ERROR_FORCING_TEST_FAULT_INJECT?

You emphasized that they are same and both for fault injection. Why not merge them into one since they are the same test?

For below 4 CCMR5F_CPUCOMP tests in your example code, you just get test result from callback function for xxx_INJECT test, and get test result from

failinfo structure for the other 3 tests.

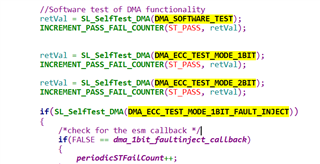

DMA is same as CCMR5F_CPUCOMP.

Besides, all the error forcing tests for SRAM/FLASH give the test result thru failinfo structure, not ESM callback function.

So can you highlight what's the difference between XXX_ERROR_FORCING_TEST and XXX_ERROR_FORCING_TEST_FAULT_INJECT?

What's the exact difference between XXX_ERROR_FORCING_TEST and XXX_ERROR_FORCING_TEST_FAULT_INJECT?

You emphasized that they are same and both for fault injection. Why not merge them into one since they are the same test?

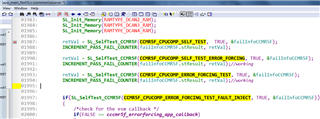

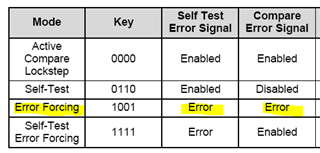

The test mechanism is same for both options. MKEY4=0x9.

But one test is in polling mode, and another is in interrupt mode (callback).

Thanks QJ.

As you said the two test options are both used to inject fault.

Firstly when we use XXX_ERROR_FORCINF_TEST as test type, the test will inject artificial 1bit/2bit ECC fault.

If the fault can be corrected the result in struct will be PASS, and if the fault can not be corrected the result will be FAIL.

At this time, the ESM interrupt can be enable or disbale to response to the correctable/uncorrectable fault . Right?

Secondly if we use XXX_ERROR_FORCING_TEST_FAULT_INJECT which means the uncorrectable fault will be injected,

the result in struct must be FAIL and the ESM interrupt must be triggerred and callbback function must be called if the ESM interrupt was enabled in advance. Right?

Firstly when we use XXX_ERROR_FORCINF_TEST as test type, the test will inject artificial 1bit/2bit ECC fault.

This option is used for CCM5F selftest. In CCM error forcing mode, a mismatched test pattern is applied to CCM-R5F (0x5 is applied to CPU1, and 0xA is applied to CPU2). After error forcing completes, the ESM error flag "CCM-R5F - CPU compare" and "CCM-R5F self-test error" is expected. If the flags are not asserted, the test failed.

At this time, the ESM interrupt can be enable or disbale to response to the correctable/uncorrectable fault . Right?

Yes. In the SDL example code, the ESM interrupt is enabled only for one of the test modes.

Secondly if we use XXX_ERROR_FORCING_TEST_FAULT_INJECT which means the uncorrectable fault will be injected,

This mode is also for CCM-R5F test. The error of injected to CCM-R5F is not correctable. The error forcing mode or error forcing test fault inject take one cycle to complete. After that, the mode is automatically switched to lockstep mode.

the result in struct must be FAIL and the ESM interrupt must be triggerred and callbback function must be called if the ESM interrupt was enabled in advance. Right?

yes.

Hi QJ,

Do you mean "CCMR5F_CPUCOMP_ERROR_FORCING_TEST" is used for CCMR5F CPU Compare fault injection

and "CCMR5F_CPUCOMP_SELF_TEST_ERROR_FORCING" is used for CCM5F selftest fault injection?

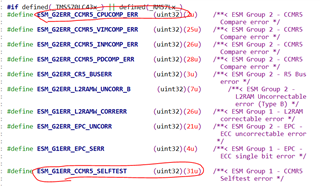

And after error forcing completes, the ESM error flag "ESM_G2ERR_CCMR5_CPUCOMP_ERR" and "ESM_G1ERR_CCMR5_SELFTEST" is expected correspondingly. Right?

If so, how about "CCMR5F_CPUCOMP_ERROR_FORCING_TEST_FAULT_INJECT" compared with "CCMR5F_CPUCOMP_ERROR_FORCING_TEST"?

Do they share the same ESM error flag "ESM_G2ERR_CCMR5_CPUCOMP_ERR"?

Besides, how about "SRAM_ECC_ERROR_FORCING_1BIT"?

There're two related ESM error flags "ESM_G1ERR_L2RAMW_CORRERR" and "ESM_G2ERR_L2RAMW_UNCORR_B". Which one will be expected after

the error "SRAM_ECC_ERROR_FORCING_1BIT" is forced completely?

If possibile, can you introduce separately how to use below 4 test options item by item? and when will the 2 ESM error flags is set? it's very confusing.

Hi,

The CPU CCM-R5F can run in one of the following four operating modes:

1. Active compare lockstep mode

2. Self-test

3. Error forcing

4. Self-test error forcing

"CCMR5F_CPUCOMP_ERROR_FORCING_TEST"

This is used for #3 error forcing mode. CCMR5F_CPUCOMP_ERROR_FORCING_TEST_FAULT_INJECT is also for #3 error forcing mode

CCMR5F_CPUCOMP_SELF_TEST_ERROR_FORCING

Is for #4 self-test error forcing mode.

And after error forcing completes, the ESM error flag "ESM_G2ERR_CCMR5_CPUCOMP_ERR" and "ESM_G1ERR_CCMR5_SELFTEST" is expected correspondingly. Right?

yes.

If so, how about "CCMR5F_CPUCOMP_ERROR_FORCING_TEST_FAULT_INJECT" compared with "CCMR5F_CPUCOMP_ERROR_FORCING_TEST"?

Do they share the same ESM error flag "ESM_G2ERR_CCMR5_CPUCOMP_ERR"?

Both of them are for #2 error forcing mode. Both selftest error and compare error are set.

Besides, how about "SRAM_ECC_ERROR_FORCING_1BIT"?

This is SRAM self-test.

There're two related ESM error flags "ESM_G1ERR_L2RAMW_CORRERR" and "ESM_G2ERR_L2RAMW_UNCORR_B". Which one will be expected after

the error "SRAM_ECC_ERROR_FORCING_1BIT" is forced completely?

ESM_G2ERR_L2RAMW_UNCORR_B is set

Hi QJ,

Do you confirm "ESM_G2ERR_L2RAMW_UNCORR_B" is set by "SRAM_ECC_ERROR_FORCING_1BIT", but not by "SRAM_ECC_ERROR_FORCING_2BIT"?

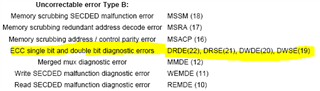

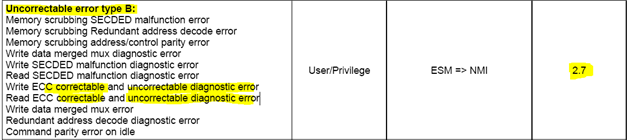

The ESM2.7 is set by both correctable ECC error and uncorrectable ECC error:

Hi QJ,

Here is the reply from Jagadish in another post.

It points out that "SRAM_ECC_ERROR_FORCING_1BIT" will trigger correctable error and "SRAM_ECC_ERROR_FORCING_2BIT" will trigger uncorrectable error.

Do you agree?

Hi Shenming,

The SRAM is protected by ECC on the data path using Single-Bit Correction Double-Bit Detection (SECDED) scheme. Any single-bit error on ECC or data is corrected automatically.

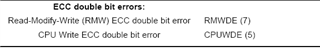

It is very easy to generate 2-bit ECC error (ESM 3.3):

1. Open CCS memory browser, display content of 0x08000000 (data), and 0x08400000 (ECC)

2. write 0x0000000000000000 to 0x08000000, the ECC ode at 0x08400000 becomes 0x0C0C0C0C0C0C0C0C

3. Disable ECC detection and correction: sl_l2ramwREG->RAMCTRL = 0x05050005;

4. Write 0x0000000000000003 to 0x08000000

5. Enable ECC detection and correction: sl_l2ramwREG->RAMCTRL = 0x0505000A;

6. read data from 0x08000000, --> generate 2-bit ECC error (ESM 3.3) and RAMErrStatus = 0x80

The SRAM selftest is to generate diagnostic ecc error: