Other Parts Discussed in Thread: HALCOGEN

Hello,

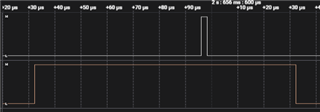

I'm working on a project, and have some interrupts enabled (SCI and SCI2 enabled using the IRQ, RTI CompareX enabled using FIQ). I'm working on adding an ESM Low interrupt handler for the ADC parity errors, but am finding some puzzling behavior. The RTI is used to set flags for function execution in the main loop, whose timing is very reliable until I enable the ESM Low Interrupt handler in the VIM. Once I enable this, it seems to break the normal execution scheme.

The function using the ADC typically executes in ~70 uSec, 40 or so of which is indicated by HalCoGen as the Sample and Conversion time for the channels being used. Once the ESM Low Interrupt is enabled, that execution time balloons to greater than 1 ms.

Other timing sees similar alteration. It seems as though the RTI interrupt itself, executed in the FIQ, is taking considerably longer to execute.

While I believe I've isolated the configuration change to the enabling of the ESM Low Interrupt, I've enabled it on the parent codebase (whose RTI interrupt lies in the IRQ, but doesn't have many of the startup tests enabled) without a similar change in timing.

Any ideas as to why this is occurring? I don't see any mention in the TRM of using the ESM low interrupt and it's impact on timing in the system, and from my understanding it seems unusual that enabling the ESM Low interrupt in the IRQ would have any impact on the execution of the RTI in the FIQ