Part Number: AM2634-Q1

Other Parts Discussed in Thread: AM2631, SYSCONFIG

Hi expert.

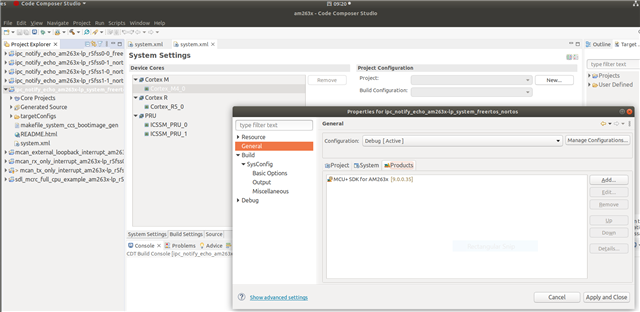

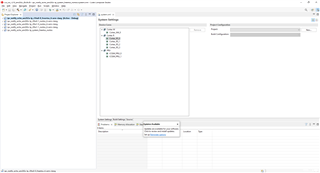

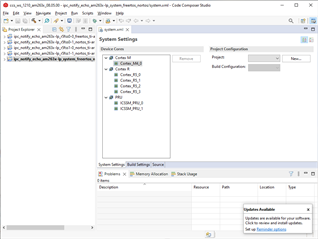

Customer reports that they have question to use syscfg tool for multicores project. They import ipc_notify_echo_am263x-lp_system_freertos_nortos from SDK8.5 and would like to modify it to enable lockstep for R5FSS1-0 & R5FSS1-1. However, system.xml only shows one R5F0-0 in syscfg editor and project property shows the chip they are using is AM2631. They can't not change it.

Is this normal?? or something wrong with syscfg?

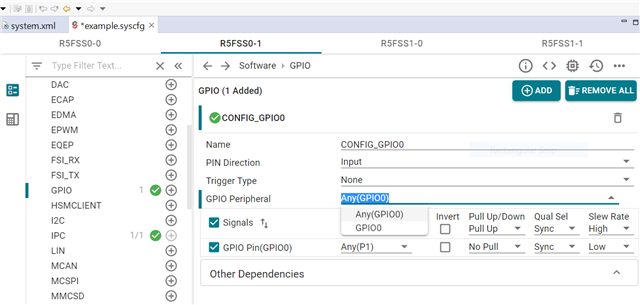

Beside, if they want to add GPIO in R5F0-1, in TRM we say we have GPIO0,1,2,3. Each core has corresponding GPIO module. But in syscfg, we only have GPIO0 can use for all cores.

Can you please check? How to fix it? or something wrong in TRM?

Regards

Andre