Other Parts Discussed in Thread: UNIFLASH, HALCOGEN

I'm working on implementing a bootloader to update an RM46 over CAN. I've based my project the example CAN bootloader provided by TI and have been reasonably successful. I'm at the stage now where having successfully written the received image to flash, I'm attempting to boot into the image. However, when I do this, I get caught in a prefetch system interrupt (address 0x1002C).

Some background information:

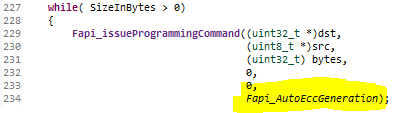

- ECC (ram) is enabled for the bootloader, however I currently have it disabled (ram & flash) for the main application.

- The Main application is an existing application that works when programed with CCS

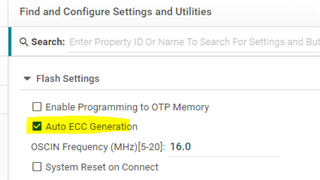

- I do not have Auto ECC Generation enabled in CCS

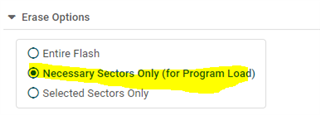

- I erase the necessary sectors only (for Program Load)

- I cannot boot the main application when I load the bootloader and the main application through Uniflash (boot to app is forced)

- I have adjusted the linker file for the main application to direct to what I believe are the correct locations.

- I have sys_intvecs.asm of the bootloader redirecting to the location of the vector for the main application in flash.

Below you'll find copies of both linker files, and attached, the HALCoGen project files.

Main App Linker cmd file:

/*----------------------------------------------------------------------------*/

/* sys_link.cmd */

/* */

/*

* Copyright (C) 2009-2018 Texas Instruments Incorporated - www.ti.com

*

*

* Redistribution and use in source and binary forms, with or without

* modification, are permitted provided that the following conditions

* are met:

*

* Redistributions of source code must retain the above copyright

* notice, this list of conditions and the following disclaimer.

*

* Redistributions in binary form must reproduce the above copyright

* notice, this list of conditions and the following disclaimer in the

* documentation and/or other materials provided with the

* distribution.

*

* Neither the name of Texas Instruments Incorporated nor the names of

* its contributors may be used to endorse or promote products derived

* from this software without specific prior written permission.

*

* THIS SOFTWARE IS PROVIDED BY THE COPYRIGHT HOLDERS AND CONTRIBUTORS

* "AS IS" AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT

* LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR

* A PARTICULAR PURPOSE ARE DISCLAIMED. IN NO EVENT SHALL THE COPYRIGHT

* OWNER OR CONTRIBUTORS BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL,

* SPECIAL, EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT

* LIMITED TO, PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES; LOSS OF USE,

* DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON ANY

* THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT

* (INCLUDING NEGLIGENCE OR OTHERWISE) ARISING IN ANY WAY OUT OF THE USE

* OF THIS SOFTWARE, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

*

*/

/* */

/*----------------------------------------------------------------------------*/

/* USER CODE BEGIN (0) */

/* USER CODE END */

/*----------------------------------------------------------------------------*/

/* Linker Settings */

--retain="*(.intvecs)"

/* USER CODE BEGIN (1) */

/* IGNORE the generated Memory code, overridden below */

#if 0

/* USER CODE END */

/*----------------------------------------------------------------------------*/

/* Memory Map */

MEMORY

{

VECTORS (X) : origin=0x00000000 length=0x00000020

FLASH0 (RX) : origin=0x00000020 length=0x0013FFE0

STACKS (RW) : origin=0x08000000 length=0x00005800

RAM (RW) : origin=0x08005800 length=0x0002a800

/* USER CODE BEGIN (2) */

#endif

/* Override Memory Segments with CRC here */

#if 1

MEMORY

{

VECTORS (X) : origin=0x00010020

length=0x00000020

vfill = 0xffffffff

CRCMEM (RX) : origin=end(VECTORS)

length=0x000001E0

vfill = 0xffffffff

FLASH0 (RX) : origin=end(CRCMEM)

length=(0x0013FFFF - end(CRCMEM))

vfill = 0xffffffff

STACKS (RW) : origin=0x08000000

length=0x00004c00

RAM (RW) : origin=0x08004c00

length=0x0002b400

#endif

#if 1

ECC_VEC (R) : origin=(0xf0400000 + (start(VECTORS) >> 3))

length=(size(VECTORS) >> 3)

ECC={algorithm=algoL2R4F021, input_range=VECTORS}

ECC_CRC (R) : origin=(0xf0400000 + (start(CRCMEM) >> 3))

length=(size(CRCMEM) >> 3)

ECC={algorithm=algoL2R4F021, input_range=CRCMEM }

ECC_FLA0 (R) : origin=(0xf0400000 + (start(FLASH0) >> 3))

length=(size(FLASH0) >> 3)

ECC={algorithm=algoL2R4F021, input_range=FLASH0 }

#endif

/* USER CODE END */

}

/* USER CODE BEGIN (3) */

/* IGNORE the generated Sections code, overridden below */

ECC

{

algoL2R4F021 : address_mask = 0xfffffff8 /* Address Bits 31:3 */

hamming_mask = R4 /* Use R4/R5 build in Mask */

parity_mask = 0x0c /* Set which ECC bits are Even and Odd parity */

mirroring = F021 /* RM57Lx and TMS570LCx are build in F021 */

}

#if 0

/* USER CODE END */

/*----------------------------------------------------------------------------*/

/* Section Configuration */

SECTIONS

{

.intvecs : {} > VECTORS

.text : {} > FLASH0

.const : {} > FLASH0

.cinit : {} > FLASH0

.pinit : {} > FLASH0

.bss : {} > RAM

.data : {} > RAM

.sysmem : {} > RAM

/* USER CODE BEGIN (4) */

#endif

/* Override Sections with CRCs here */

#if 1

SECTIONS

{

.intvecs : {} > VECTORS, crc_table( _crc_table, algorithm=CRC32_C )

.text align(32) : {} > FLASH0, crc_table( _crc_table, algorithm=CRC32_C )

.const align(32) : {} > FLASH0, crc_table( _crc_table, algorithm=CRC32_C )

.cinit align(32) : {} > FLASH0, crc_table( _crc_table, algorithm=CRC32_C )

.pinit align(32) : {} > FLASH0

.bss : {} > RAM

.data : {} > RAM

.sysmem : {} > RAM

.TI.crctab : {} > CRCMEM

#endif

/* USER CODE END */

}

/* USER CODE BEGIN (5) */

/* USER CODE END */

/*----------------------------------------------------------------------------*/

/* Misc */

/* USER CODE BEGIN (6) */

/* USER CODE END */

/*----------------------------------------------------------------------------*/

Bootloader Linker Cmd File:

/* Copyright (C) 2013-2019 Texas Instruments Incorporated - http://www.ti.com/

*

*

* Redistribution and use in source and binary forms, with or without

* modification, are permitted provided that the following conditions

* are met:

*

* Redistributions of source code must retain the above copyright

* notice, this list of conditions and the following disclaimer.

*

* Redistributions in binary form must reproduce the above copyright

* notice, this list of conditions and the following disclaimer in the

* documentation and/or other materials provided with the

* distribution.

*

* Neither the name of Texas Instruments Incorporated nor the names of

* its contributors may be used to endorse or promote products derived

* from this software without specific prior written permission.

*

* THIS SOFTWARE IS PROVIDED BY THE COPYRIGHT HOLDERS AND CONTRIBUTORS

* "AS IS" AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT

* LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR

* A PARTICULAR PURPOSE ARE DISCLAIMED. IN NO EVENT SHALL THE COPYRIGHT

* OWNER OR CONTRIBUTORS BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL,

* SPECIAL, EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT

* LIMITED TO, PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES; LOSS OF USE,

* DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON ANY

* THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT

* (INCLUDING NEGLIGENCE OR OTHERWISE) ARISING IN ANY WAY OUT OF THE USE

* OF THIS SOFTWARE, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

*/

/* */

/*----------------------------------------------------------------------------*/

/* USER CODE BEGIN (0) */

/* USER CODE END */

/*----------------------------------------------------------------------------*/

/* Linker Settings */

--retain="*(.intvecs)"

/* USER CODE BEGIN (1) */

/* USER CODE END */

/*----------------------------------------------------------------------------*/

/* Memory Map */

MEMORY

{

/* Bank 0 (384kB) */

VECTORS (X) : origin=0x00000000

length=0x00000020

vfill = 0xFFFFFFFF

FLASH0 (RX) : origin=end(VECTORS)

length=(0x00140000 - size(VECTORS))

vfill = 0xFFFFFFFF

SRAM (RW) : origin=0x08002000

length=0x0002D000

STACKS (RW) : origin=0x08000000

length=0x00002000

/* USER CODE BEGIN (2) */

#if 1

/* Bank 0 ECC */

ECC_VEC (R) : origin=(0xf0400000 + (start(VECTORS) >> 3))

length=(size(VECTORS) >> 3)

ECC={algorithm=algoL2R4F021, input_range=VECTORS}

ECC_FLA0 (R) : origin=(0xf0400000 + (start(FLASH0) >> 3))

length=(size(FLASH0) >> 3)

ECC={algorithm=algoL2R4F021, input_range=FLASH0 }

#endif

/* USER CODE END */

}

/* USER CODE BEGIN (3) */

ECC

{

algoL2R4F021 : address_mask = 0xfffffff8 /* Address Bits 31:3 */

hamming_mask = R4 /* Use R4/R5 build in Mask */

parity_mask = 0x0c /* Set which ECC bits are Even and Odd parity */

mirroring = F021 /* RM57Lx and TMS570LCx are build in F021 */

}

/* USER CODE END */

/*----------------------------------------------------------------------------*/

/* Section Configuration */

SECTIONS

{

.intvecs : {} > VECTORS

flashAPI:

{

./Fapi_UserDefinedFunctions.obj (.text)

./bl_flash.obj (.text)

--library= "/home/fw/fwbl/flashAPI/F021_API_CortexR4_LE.lib" (.text)

} palign=8 load = FLASH0, run = SRAM, LOAD_START(apiLoadStart), RUN_START(apiRunStart), SIZE(apiLoadSize)

.text : {} > FLASH0 /*Initialized executable code and constants*/

.const : {} palign=8 load=FLASH0, run = SRAM, LOAD_START(constLoadStart), RUN_START(constRunStart), SIZE(constLoadSize)

.cinit : {} > FLASH0 /*Initialized global and static variables*/

.pinit : {} > FLASH0

.data : {} > SRAM

.bss : {} > SRAM /*Uninitialized Global and static variables */

.sysmem : {} > SRAM

/* USER CODE BEGIN (4) */

/* USER CODE END */

}

/* USER CODE BEGIN (5) */

/* USER CODE END */

Bootloader sys_intvecs.asm

;-------------------------------------------------------------------------------

; sys_intvecs.asm

;

; Copyright (C) 2009-2018 Texas Instruments Incorporated - www.ti.com

;

;

; Redistribution and use in source and binary forms, with or without

; modification, are permitted provided that the following conditions

; are met:

;

; Redistributions of source code must retain the above copyright

; notice, this list of conditions and the following disclaimer.

;

; Redistributions in binary form must reproduce the above copyright

; notice, this list of conditions and the following disclaimer in the

; documentation and/or other materials provided with the

; distribution.

;

; Neither the name of Texas Instruments Incorporated nor the names of

; its contributors may be used to endorse or promote products derived

; from this software without specific prior written permission.

;

; THIS SOFTWARE IS PROVIDED BY THE COPYRIGHT HOLDERS AND CONTRIBUTORS

; "AS IS" AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT

; LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR

; A PARTICULAR PURPOSE ARE DISCLAIMED. IN NO EVENT SHALL THE COPYRIGHT

; OWNER OR CONTRIBUTORS BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL,

; SPECIAL, EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT

; LIMITED TO, PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES; LOSS OF USE,

; DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON ANY

; THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT

; (INCLUDING NEGLIGENCE OR OTHERWISE) ARISING IN ANY WAY OUT OF THE USE

; OF THIS SOFTWARE, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

;

;

;

.sect ".intvecs"

.arm

;-------------------------------------------------------------------------------

; import reference for interrupt routines

.ref _c_int00

;-------------------------------------------------------------------------------

; interrupt vectors

; Please change the #0x???? for your specified image location defined in bl_config.h - 0x08

b _c_int00 ;0x00

b #0x10018 ;0x04 UNDEF; 0x10000-0x08

b #0x10018 ;0x08 SVC ; 0x10000-0x08

b #0x10018 ;0x0C PABT ; 0x10000-0x08

b #0x10018 ;0x10 DABT ; 0x10000-0x08

reservedEntry

b reservedEntry ;0x14, reserved

b #0x10018 ;0x18, irqDispatcher

ldr pc,[pc, #-0x1b0] ;0x1C, FIQ

;-------------------------------------------------------------------------------