Hello,

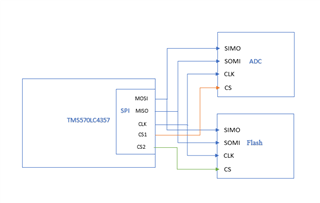

We need to write data to an SPI flash using DMA. The DMA is also used by several other SPI peripherals like an ADC.

We need to update the DMA control packet to configure the source address and element count for each transfer for SPI flash data write.

We would also like to maintain DMA enabled while updating the control packet, as other SPI peripherals are running(specially, we need a continuous ADC acquisition while writing to flash)

According to TRM (SPNU563A), p. 724, table 20-9, in the description of the DMA_EN bit, I understand that the control packet should be set before enabling the DMA controller.

This would force us to disable DMA before configuring the control packet.

We would like to find a way to update the control packet without disabling DMA, if is possible.

Could you tell use which conditions shall be fulfilled to update a DMA control packet while DMA is still enabled?

I was thinking about to ensure first that DMA was not busy (MA_REG_BASE_ADDR->GCTRL & MASK_DMA_GCTRL_BUS_BUSY == 0), and then write the control packet (DMA_RAM_REG_BASE_ADDR->PCP[channel])

Would that work or shall we also check other conditions?