We have a custom board using the TM4C1292NCPDT.

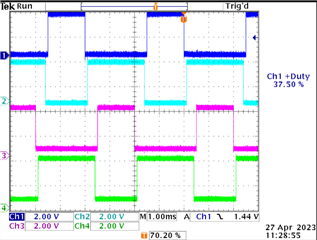

The board will be using two interleaved PWM signal pairs. Currently, I am running PWM Gen 0 and PWM Gen 1 in UP-DOWN mode. Is there a way to offset the generator blocks so they are 180 degrees out of phase using the TI SW API? For example, in the image below, I want L1 and L2 to be 180 degrees out of phase and H1 and H2 to be 180 degrees out of phase, while retaining the same duty cycles. Is there a way in the SW API to set the starting count of one of the generators to accomplish this? The duty cycle will change during runtime, so it needs to be a true, 180 degree phase shift (instead of inverting a 50% duty cycle signal).

Here is the corresponding init code:

#define GENERATOR_PERIOD_COUNTS 1000 #define DEAD_BAND_DURATION_COUNTS 50 SysCtlPeripheralEnable(SYSCTL_PERIPH_GPIOF); while(!SysCtlPeripheralReady(SYSCTL_PERIPH_GPIOF)); // Configure the GPIO for PWM peripheral use. GPIOPinConfigure(GPIO_PF0_M0PWM0); GPIOPinConfigure(GPIO_PF1_M0PWM1); GPIOPinConfigure(GPIO_PF2_M0PWM2); GPIOPinConfigure(GPIO_PF3_M0PWM3); GPIOPinTypePWM(GPIO_PORTF_BASE, GPIO_PIN_0); GPIOPinTypePWM(GPIO_PORTF_BASE, GPIO_PIN_1); GPIOPinTypePWM(GPIO_PORTF_BASE, GPIO_PIN_2); GPIOPinTypePWM(GPIO_PORTF_BASE, GPIO_PIN_3); SysCtlPeripheralEnable(SYSCTL_PERIPH_PWM0); // enable the pwm peripheral while(!SysCtlPeripheralReady(SYSCTL_PERIPH_PWM0)); // wait for the peripheral to be ready PWMClockSet(PWM0_BASE, PWM_SYSCLK_DIV_1); // Sets the PWM clock configuration to use the system clock with a divider of 1 /* * Configure generator blocks to run in up/down mode which allows * use of the built-in dead band time. In this mode, the synchronization of * the 2 signals in each generator are synchronized by default, so we * don't need to set any. */ PWMGenConfigure(PWM0_BASE, PWM_GEN_0, PWM_GEN_MODE_UP_DOWN | PWM_GEN_MODE_NO_SYNC); PWMGenConfigure(PWM0_BASE, PWM_GEN_1, PWM_GEN_MODE_UP_DOWN | PWM_GEN_MODE_NO_SYNC); /* * Set the PWM period. Configures the reference counter that counts in up/down mode. * * f = PWM_ref_clk / N ... where f is the desired frequency, N is the passed param, * and PWM_ref_clk is the reference clock. */ PWMGenPeriodSet(PWM0_BASE, PWM_GEN_0, GENERATOR_PERIOD_COUNTS); PWMGenPeriodSet(PWM0_BASE, PWM_GEN_1, GENERATOR_PERIOD_COUNTS); /* * Enables dead band generation with a configurable buffer on both the rising and falling * edge of the signals. Enabling this will automatically synchronize the signal pairs in * each of the generator blocks. */ PWMDeadBandEnable(PWM0_BASE, PWM_GEN_0, DEAD_BAND_DURATION_COUNTS, DEAD_BAND_DURATION_COUNTS); PWMDeadBandEnable(PWM0_BASE, PWM_GEN_1, DEAD_BAND_DURATION_COUNTS, DEAD_BAND_DURATION_COUNTS); PWMPulseWidthSet(PWM0_BASE, PWM_OUT_0, 550); // complement signal PWM_OUT_1 updates automatically PWMPulseWidthSet(PWM0_BASE, PWM_OUT_2, 550); // complement signal PWM_OUT_3 updates automatically PWMGenEnable(PWM0_BASE, PWM_GEN_0); PWMGenEnable(PWM0_BASE, PWM_GEN_1); PWMSyncTimeBase(PWM0_BASE, PWM_GEN_1_BIT | PWM_GEN_0_BIT); PWMOutputState(PWM0_BASE, PWM_OUT_2_BIT | PWM_OUT_3_BIT | PWM_OUT_0_BIT | PWM_OUT_1_BIT, true);