Part Number: AM2434

Hi,

I am planning to use AM2434BSDGHIALVR for my new project.

Kindly help me resolve the below queries.

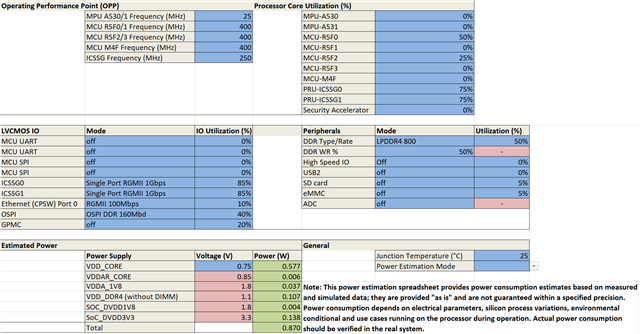

- Is it possible to reduce the power consumption up to a level of 0.5W with two 1G ethernet active?

- We need to use two 1G ethernet with PROFINET. What are the major things we need to take care in Hardware/Firmware?

- What should be the minimum MCU clock frequency to achieve the proper 1G ethernet communication

- Will there heat sink required for AM2434BSDGHIALVR when the active peripherals are only

1) Two RGMII with profinet

2) DDR4

3) Boot Flash

Thanks in advance

Melbin