Other Parts Discussed in Thread: HALCOGEN

Hi,

Can you help find the below ESM error defintions in some data sheet?

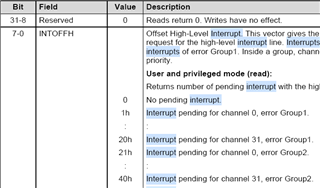

Or illustrate how to set the esmREG->IOFFHR/esmREG->IOFFLR registers for ESM module to select the channel? Thanks.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi Jagadish,

Same question as above.

We just do the Flash ECC 2bit error forcing test as below:

1. run the API funtion with test type "FLASH_ECC_TEST_MODE_2BIT".

retVal = SL_SelfTest_Flash(FLASH_ECC_TEST_MODE_2BIT, TRUE, &failInfoFlash);

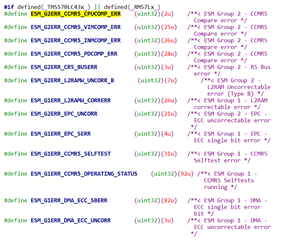

2. The below ESM error will be expected. Right?

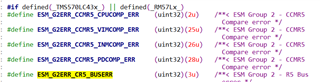

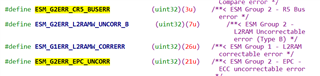

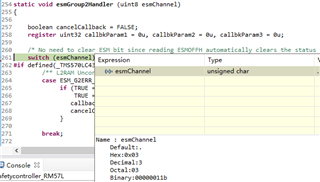

3. But an unexpected interrupt type "ESM_G2ERR_CR5_BUSERR" occurred as below:

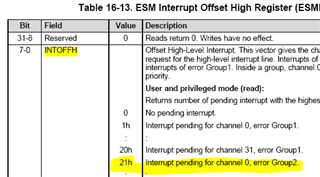

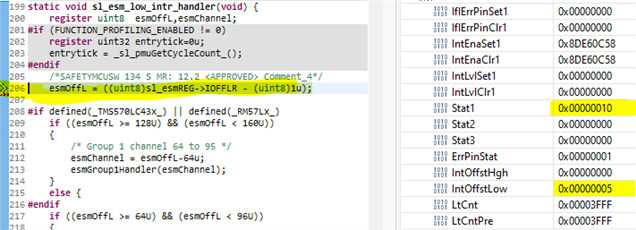

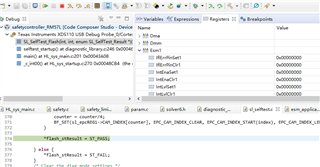

4. By debuging with CCS, we find the value of register esmREG->IOFFHR turn to be "36" and the channel of ERR Group2 turn to be "36-1-32=3" after error injection with "FLASH_ECC_TEST_MODE_2BIT".

The question is how the register "esmREG->IOFFHR" was set with "36", and how to make it to be "54" to make channel to be ""54-1-32=21" as expected value. We must have done something wrong during the fault injection test.

By further investigation, we found the root cause why the register "esmREG->IOFFHR" was set with "36".

If we mark below code, the ESM interrupt of Group2 Channel3 will disappear.

We are eager to know how to make it to be "54" to make channel to be ""54-1-32=21" as expected value.

Besides, SRAM/CCMR5F fault injection also can not trigger corresponding ESM interrupts.

Now, our test task has been suspended due to this issue.

Here is the related source code provided by TI, please help check it as soon as possible. Thanks so much.

2. The below ESM error will be expected. Right?

SL_SelfTest_Flash(FLASH_ECC_TEST_MODE_2BIT, TRUE, &failInfoFlash); -- > ESM 2.3 will be set.

SL_SelfTest_Flash(FLASH_ECC_TEST_MODE_1BIT, TRUE, &failInfoFlash); -- > ESM 1.4 will be set.

4. By debuging with CCS, we find the value of register esmREG->IOFFHR turn to be "36"

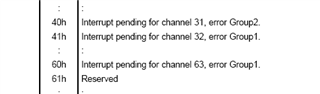

It is ESM 2.3 --> 21h + 3 = 36

Hi QJ,

1. Why does FLASH_ECC_TEST_MODE_2BIT trigger ESM2.3, but not ESM2.21? In other post, Jagadish confirmed FLASH_ECC_TEST_MODE_2BIT will trigger ESM2.21.

2. By our test, no matter what test type we select for function SL_SelfTest_Flash, it always triggers ESM2.3(esmREG->IOFFHR turn to be "36" ).

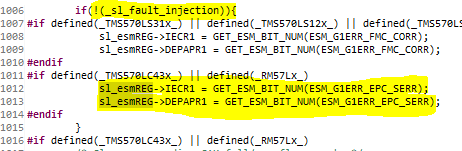

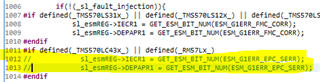

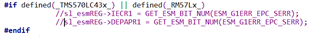

It's because we add below code. If we mark it, ESM2.3 will not be triggered as well.

3. Please help check your code as below. Thanks so much!!

We are eager to know how to make it to be "54" to make channel to be ""54-1-32=21" as expected value.

ESM 1.54 --> 41h +54-32 = 41h+22 = 87

If esmREG->IOFFHR = 54 = 36h --> 36h - 21h = 15h = 21 --> ESM 2.21

I known. You don't mention how to set esmREG->IOFFHR with "54".

I have searched carefully in your diagnostic library source code and related API funtions, there's no register esmREG->IOFFHR related operation in sl_selftest.c at all.

Have you tested all the APIs and verified their usability on RM57L843 device? Thanks a lot.

esmREG->IOFFHR with "54".

This register is read only, we can not set this esmREG->IOFFHR to "54" manually.

Have you tested all the APIs and verified their usability on RM57L843 device?

SDL development team tested all the APIs before SDL was released. But I didn't test all the APIs.

Thanks QJ,

I have known how to get current channel number for interrupt function. But I don't know how to trigger the ESM interrupt with correct channel number predefined in source code after implementing corresponding fault injection. What's the trigger mechanism?

We can't trigger the corresponding ESM interrupt as expected after error forcing test using the API provided by TI.

Can you help check the code or provide the new realization for fault injection? Thanks so much.

The ESM consists of 3 groups. The group 3 errors always generate an nERROR pin output. The group 2 errors always generate a high priority interrupt (VIM channel 0), and the group 1 errors have a configurable interrupt response (enable or disable, low priority or high priority).

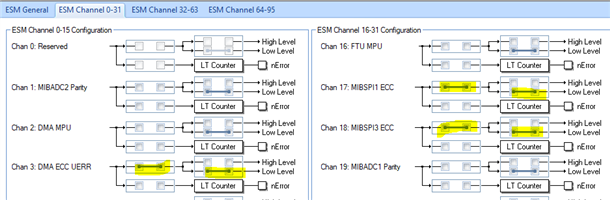

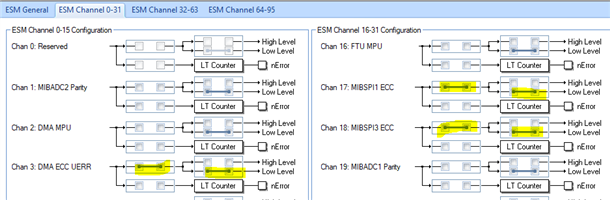

The interrupt for group 1 error is enabled using: ESMIESR1/4/7 registers, and interrupt priority is controlled by ESMILSR1/4/7 registers. You can use HALCoGen to configure the ESM interrupt:

For fault injection option, the ESM interrupt is enabled, so interrupt is generated when an error is injected:

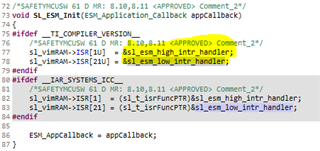

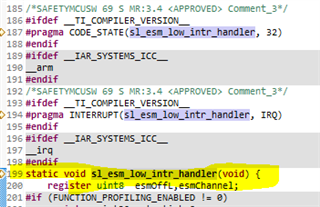

The ESM interrupt handlers are defined by:

But the SDL doesn't have fault injection option for flash 1-bit ECC selftest. SO to enable the interrupt, please comment the following statements out:

Hi QJ,

1. Can you confirm if we need mark the code as below to do fault injection for RM57?

Because if we don't mark it, any calling of SL_SelfTest_Flash will always trigger ESS2.3 fault, no matter what type the parameter is, or even if the parameter is empty.

2. After we marked the code mentioned in step1, let us do the flash ecc 1bit error forcing test.

According to you advice, I marked the code as below, but corresponding ESM Group1 interrupt still did not occur.

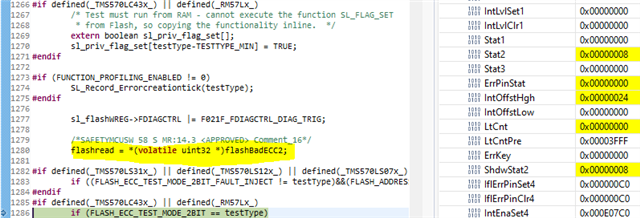

By debugging with CCS, the key handling of fault insertion has been executed:

3. After we marked the code mentioned in step1 and step2, let us do the flash ecc 2bit error forcing test.

At the beginning, corresponding ESM Group2 interrupt still did not occur.

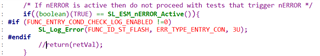

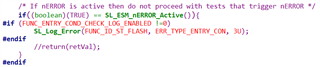

But if we continue to mark the "return" line when detecting nERROR is active, the ESM Group2 interrupt was triggered.

Why not procee with tests that trigger nERROR in the test code if nERROR is active?

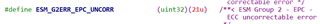

By debugging with CCS, we find the channel number is still "3" which means the fault type is "ESM_G2ERR_CR5_BUSERR".

Can you confirm whether or not the fault shoule be "ESM_G2ERR_CR5_BUSERR", after we perform "FLASH_ECC_TEST_MODE_2BIT" fault injection?

Isn't the interrupt type of ESM Group "ESM_G2ERR_EPC_UNCORR"?

To save time, could you please answer all my questions at once? Thanks a lot.

1. Can you confirm if we need mark the code as below to do fault injection for RM57?

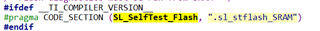

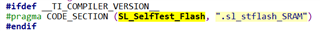

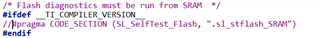

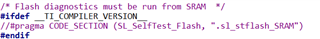

For RM57Lx, the flash selftest should be executed from SRAM.

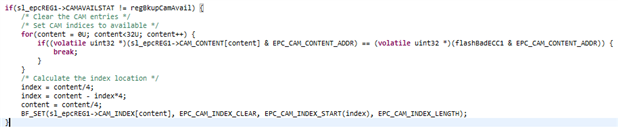

There is a software bug in sl_selftest_flash() function:

The original code is:

The workaround:

if(sl_epcREG1->CAMAVAILSTAT != regBkupCamAvail) {

unsigned int counter = 0;

for(content = 0U; content<32U; content++) {

if((volatile uint32 )(sl_epcREG1->CAM_CONTENT[content] & EPC_CAM_CONTENT_ADDR) == (*volatile uint32 *)(flashBadECC1 & EPC_CAM_CONTENT_ADDR)) {

break;

}

counter ++;

}

/* Calculate the index location */

index = counter/4;

index = counter - index*4;

counter = counter/4;

BF_SET(sl_epcREG1->CAM_INDEX[*counter*], EPC_CAM_INDEX_CLEAR, EPC_CAM_INDEX_START(index), EPC_CAM_INDEX_LENGTH);

}

2. After we marked the code mentioned in step1, let us do the flash ecc 1bit error forcing test.

According to you advice, I marked the code as below, but corresponding ESM Group1 interrupt still did not occur.

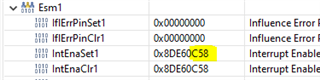

Please make sure that the bit 4 of IntEnaSet1 is set:

I just run the test, and got the ESM interrupt:

3. After we marked the code mentioned in step1 and step2, let us do the flash ecc 2bit error forcing test.

At the beginning, corresponding ESM Group2 interrupt still did not occur.

My test shows that the interrupt is generated, and nERROR becomes active (ErrPinStat=0x0):

intOffstHigh = 0x24 --> ESM 2.3 -- Cortex-R5F Core - All fatal bus error events. [Commonly caused by improper or incomplete ECC values in Flash.]

Hi QJ,

Two things must be highlighted. They must be resolved before formal fault injection with passing specific test type.

1. If we keep below handling effective, running SL_SelfTest_Flash will always trigger ESS2.3 fault no matter what the test type is, even if the function body is empty.

2. The nERROR has been active each time before formal fault injection. So we can't proceed with the test if we don't mark it.

Why is that? Is it activated in initial phase?

About formal fault injection test:

1.After marking the two places mentioned above, I started the fault injection test "FLASH_ECC_TEST_MODE_1BIT".

But the bit 4 of IntEnaSet1 is not set until all the test program is completed.

2. If "FLASH_ECC_TEST_MODE_2BIT" do trigger "ESM_G2ERR_CR5_BUSERR"(ESM2.3) as you confirmed above,

which fault injection will trigger "ESM_G2ERR_EPC_UNCORR"(ESM2.21)?

1. If we keep below handling effective, running SL_SelfTest_Flash will always trigger ESS2.3 fault no matter what the test type is, even if the function body is empty.

It is required to run the flash self-test from SRAM rather than from flash. The purpose of this statement is to allocate a memory space for SL_Selftest_Flash() function. Please don't comment this statement out. Thanks

2. The nERROR has been active each time before formal fault injection. So we can't proceed with the test if we don't mark it.

Why is that? Is it activated in initial phase?

If you run the flash selftest from flash, the ESM 2.3 may be triggered and nError is asserted. Before running flash selftest, please make sure that no ESM error flag is set, for example ESM 2.3.

If any ECC error such as ESM2.3, please fix the error before doing the selftest.

2. If "FLASH_ECC_TEST_MODE_2BIT" do trigger "ESM_G2ERR_CR5_BUSERR"(ESM2.3) as you confirmed above,

which fault injection will trigger "ESM_G2ERR_EPC_UNCORR"(ESM2.21)?

Fult injection (SRAM, flash) doesn't generate ESM 2.21 error.

Hi QJ,

1. QJ:Before running flash selftest, please make sure that no ESM error flag is set, for example ESM 2.3.

What did you mean "selftest"? I just do error forcing test "FLASH_ECC_TEST_MODE_1BIT/FLASH_ECC_TEST_MODE_2BIT", no "selftest".

I have reset the nERROR flag by running "esmTriggerErrorPinReset" before each error forcing test and there's no nERROR activation any more.

2. QJ:Fult injection (SRAM, flash) doesn't generate ESM 2.21 error.

Which fault injection will generate ESM 2.21 error(EPC ECC uncorrectable error)? In other post, Jagadish confirmed "FLASH_ECC_TEST_MODE_2BIT" fault injection will trigger "ESM_G2ERR_EPC_UNCORR".

3. Where to find and check the mapping code generated from below configuration?

Because "FLASH_ECC_TEST_MODE_1BIT" error forcing always triggers ESM2.3 interrupt as same as "FLASH_ECC_TEST_MODE_2BIT".

I want to check the original configuration.

What did you mean "selftest"?

Before calling SL_Selftest_Flash(...), checking the ESM ESM Registers. The status register 1/4/7 are for ESM group1. The status register 2 is for group 2. The status register 3 is for group 3.

3. Where to find and check the mapping code generated from below configuration?

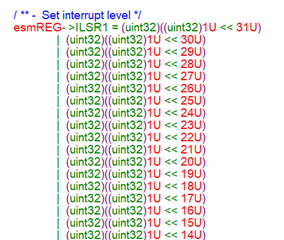

They are enabled in esmInit()

Hi QJ,

1. You missed the second question listed above:

Since "FLASH_ECC_TEST_MODE_2BIT" generates "ESM_G2ERR_CR5_BUSERR", which fault injection will generate "ESM_G2ERR_EPC_UNCORR"?

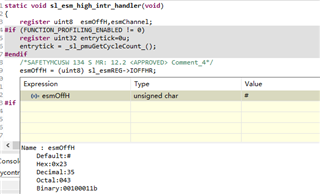

2. "FLASH_ECC_TEST_MODE_1BIT" error forcing can generate ESM group1 interrupt "ESM_G1ERR_EPC_SERR" normallly.

Function "sl_esm_high_intr_handler" was called after I set esmREG->ILSR1 into "1".

1. "FLASH_ECC_TEST_MODE_1BIT" --> ESM 1.4 is set

2. "FLASH_ECC_TEST_MODE_2BIT" --> ESM 2.3 should be set. But I didn't get this bit set.

Function "sl_esm_high_intr_handler" was called after I set esmREG->ILSR1 into "1".

This is expected.