Part Number: TM4C123GE6PM

Other Parts Discussed in Thread: EK-TM4C123GXL

Hello,

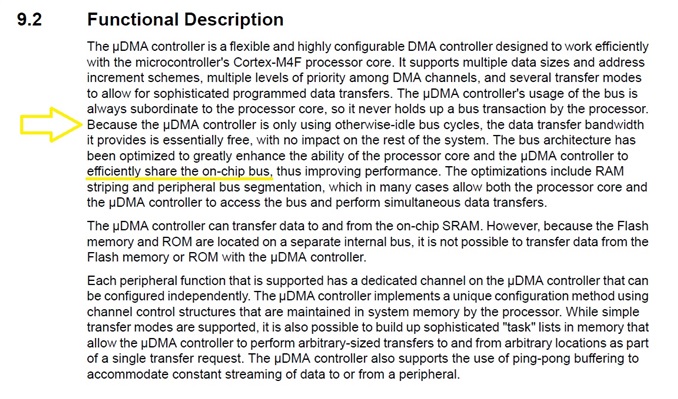

I have a general question about how the uDMA and CPU share the bus. I've been reading the datasheet to try to wrap my head around this. In section 9.2 "Functional Description" shown below it says that the uDMA uses spare CPU cycles. I'm having trouble getting a good understanding of what this means - especially for a case like ping pong data blocks from say SSI RX FIFO to a chunk of memory which is my use case.

My application has the CPU in a main loop checking variables in memory while the uDMA should be moving data from SSI RS to a memory area with an arbitration size of 4 bytes. I thought the CPU and uDMA shared the same bus to memory so my questions are below.

1. Does the DMA only access memory when the CPU isn't? So if I'm constantly polling a flag in RAM will that inhibit the performance of the DMA due to reading the flag (memory location)?

2. How do I know when the CPU is throttling the DMA or vice versa? I'm confused here as I have read they share one bus but the uDMA often uses spare CPU cycles?

Thanks