Part Number: AM2634

Hi,

I am looking for a software example that starts the slave cores from the master core through software for AM2634

Where I can find it ?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Part Number: AM2634

Hi,

I am looking for a software example that starts the slave cores from the master core through software for AM2634

Where I can find it ?

Hi Tareq,

The AM263x R5F_0_0 does play a important role during the bootloading phase, but after that each core runs by itself. There is no concept of the master and slave R5F cores in that sense. The program and the data sections for each core are loaded into on chip memory during the bootloading phase (done by R5F_0_0), but after that each core runs independently. R5F cores can use the IPC to communicate to one another. Please refer to the following UARLs for details:

AM263x MCU+ SDK: Understanding the bootflow and bootloaders (ti.com) for bootlaoding process and requirements.

AM263x MCU+ SDK: Understanding inter-processor communication (IPC) for intercore communication.

Best regards,

Ming

This because I am running an AUTOSAR application and in AUOTSAR the master core should trigger the start for the remain cores

Hi Tareq,

It is possible, but you will need to modify (or customize) the current SBL_OSPI example in the MCU+ SDK. The current SBL_OSPI example runs on the R5F_0_0. It loads the application code for all cores and then start each core one by one. Before the R5F_0_0 starts other cores, the other cores are in WFI state.

Best regards,

Ming

Hi Tareq,

The boot process for AM263x is the same. Refer to the following URL for the AM263x boot process:

AM263x MCU+ SDK: Understanding the bootflow and bootloaders (ti.com)

AM263x MCU+ SDK: SBL QSPI (ti.com)

The SBL_QSPI example is at:

C:\ti\mcu_plus_sdk_am263x_08_06_00_34\examples\drivers\boot\sbl_qspi

The line 129 - 146 of main.c is where the R5F cores are started one by one.

Best regards,

Ming

Thanks Ming for your reply. This is provided some insights

As I mentioned I am developing an operating system and in my testing environment I am not using SBL so T32 scripts helps me to boot R5F_0_0 core and I guess what I need to do in my software is to unhalt the other cores like the example sbl_qspi (The software is fleshed in other cores also by T32 scripts)

I tried to do so but unhalt do nothing and software in other core still stuck in its entry point.

Not sure if they already in WFI state or not.

I have read the link: AM263x MCU+ SDK: Understanding the bootflow and bootloaders (ti.com)

It mentions "the very first thing it does is detect the core and continue execution for Core0, while if the core is Core1 then it enters wfi loop."

how entering wfi loop is done in this case ? note that MSS_CTRL_R5SS0_FORCE_WFI register is global for whole R5SS0.

Hi Tareq,

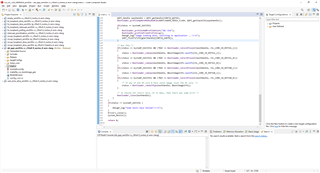

Is your CPU already in WFI ? you can check the same via this -

Best Regards,

Aakash

Hi Tareq,

Are you using DEV Boot Mode ? In that case you can control all the initialization via Debugger. If you are doing all the initialization via debugger, can you share your .cmm file ?

Best Regards,

Aakash

I am using QSPI mode but I am flashing all my application in RAM as this is enough for testing purposes.

How can I send you the cmm scripts as I cannot see an attachment option here

This an inital example trying to run R5F_SS0 as dual core where core0 is the master and core 1 is the slave core

LOCAL ¶meter_list

ENTRY %LINE ¶meter_list

DO "~~~~/scripts/AM263x.cmm" ; enable all power & clocks & load menus

DO "~~~~/scripts/AM263x.cmm" R5F_SS0_Dual_Core_RAM_boot

DO "~~~~/scripts/AM263_Common.cmm" R5F_SS0_POR_Reset

RESet

SYNCH.RESet

SYStem.RESet

IF COMBIPROBE()||UTRACE()

SYStem.CONFIG.CONNECTOR MIPI34 ; because of converter LA-3782

SYStem.Option RESBREAK OFF

SYStem.Option EnReset OFF

SYStem.JTAGCLOCK CTCK 10MHz

SYStem.MemAccess.DAP

SYStem.Option.imaskasm.on

SYStem.Option.IMASKHLL.ON

TPIU.PortMode.Continuous

IF !SIMULATOR()

trace.method.Onchip

&intercomport_core0=FORMAT.DECIMAL(1.,intercom.port())

&intercomport_core1=FORMAT.DECIMAL(1.,intercom.port()+1)

&core0="intercom localhost:&intercomport_core0"

&core1="intercom localhost:&intercomport_core1"

&allcores="GOSUB intercom_allcores "

; set titles

&core0 Title "CORE0"

&core1 Title "CORE1"

&core0 area.create A000 100 1000

&core0 area

&core1 area.create A000 100 1000

&core1 area

&core0 SYStem.Mode Down

&core0 SYStem.CPU Am2634-SS0

&core0 core.assign 1

&core0 SYStem.Mode Attach

&core0 break

&core0 Register.Init

&core1 SYStem.Mode Down

&core1 SYStem.CPU Am2634-SS0

&core1 core.assign 2

&core1 SYStem.Mode Attach

&core1 break

&core1 Register.Init

;Disable MPU

&core0 Data.Set C15:0x1 %long (Data.Long(C15:0x1)&(~0x1))

&core1 Data.Set C15:0x1 %long (Data.Long(C15:0x1)&(~0x1))

;Load elf

&core0 data.load.elf ¶meter_list

&core1 data.load.elf ¶meter_list

;Turn Off Vector Catches

&core0 TrOnchip.Set.FIQ OFF

&core0 TrOnchip.Set.IRQ OFF

&core0 TrOnchip.Set.DABORT OFF

&core0 TrOnchip.Set.PABORT OFF

&core0 TrOnchip.Set.SWI OFF

&core0 TrOnchip.Set.UNDEF OFF

&core0 TrOnchip.Set.RESET OFF

&core1 TrOnchip.Set.FIQ OFF

&core1 TrOnchip.Set.IRQ OFF

&core1 TrOnchip.Set.DABORT OFF

&core1 TrOnchip.Set.PABORT OFF

&core1 TrOnchip.Set.SWI OFF

&core1 TrOnchip.Set.UNDEF OFF

&core1 TrOnchip.Set.RESET OFF

; Enable run time accesses to R5 TCMs

&core0 DO "~~~~/scripts/am263_runtime_memory_access.cmm"

R5F_SS0_Dual_Core_RAM_boot:

(

DO "&path_AM263_common_cmm" MSS_CTRL_unlock

ENTRY &__V7

DO "&path_AM263_common_cmm" MSS_TOPRCM_unlock

ENTRY &__V8

DO "&path_AM263_common_cmm" MSS_RCM_unlock

ENTRY &__V9

DO "&path_AM263_PLL_cmm" Config_R5FCLK_400M_SYSCLK_200M

ENTRY &__V10

GOSUB En_All_Peripheral_Clks

DO "&path_AM263_common_cmm" R5F_SS0_Reset

ENTRY &__V12

DO "&path_AM263_common_cmm" R5F_SS1_Reset

ENTRY &__V13

DO "&path_AM263_common_cmm" R5F_ROM_eclipse

ENTRY &__V14

DO "&path_AM263_common_cmm" R5F_SS0_CoreA_unhalt

ENTRY &__V15

DO "&path_AM263_common_cmm" R5F_SS0_CoreB_unhalt

ENTRY &__V16

DO "&path_AM263_common_cmm" R5F_SS1_CoreA_unhalt

ENTRY &__V17

DO "&path_AM263_common_cmm" R5F_SS1_CoreB_unhalt

ENTRY &__V18

PRINT ""

PRINT ""

PRINT " ***All R5F cores are in Dual core RAM boot mode*** "

PRINT ""

PRINT ""

RETURN

)

R5F_SS0_POR_Reset:

(

GOSUB Write_MMR (&__MSS_RCM_U_BASE+&__MSS_RCM_R5SS0_POR_RST_CTRL) 0x7

GOSUB Write_MMR (&__MSS_RCM_U_BASE+&__MSS_RCM_R5SS0_POR_RST_CTRL) 0x0

PRINT ""

PRINT "*R5FSS0 POR Complete*"

PRINT ""

RETURN

)

R5F_SS0_Reset:

(

GOSUB Write_MMR (&__MSS_RCM_U_BASE+&__MSS_RCM_R5SS0_RST2ASSERTDLY) 0x0

GOSUB Write_MMR (&__MSS_RCM_U_BASE+&__MSS_RCM_R5SS0_RST_WFICHECK) 0x00000707

GOSUB Write_MMR (&__MSS_CTRL_U_BASE+&__MSS_CTRL_R5SS0_CONTROL) 0x707

GOSUB Write_MMR (&__MSS_CTRL_U_BASE+&__MSS_CTRL_R5SS0_CONTROL) 0x700

GOSUB Write_MMR (&__MSS_CTRL_U_BASE+&__MSS_CTRL_R5SS0_CONTROL) 0x70700

GOSUB Write_MMR (&__MSS_CTRL_U_BASE+&__MSS_CTRL_R5SS0_FORCE_WFI) 0x7

PRINT ""

PRINT ""

PRINT "***R5FSS0 Reset Complete***"

PRINT ""

RETURN

)

R5F_ROM_eclipse:

(

GOSUB Write_MMR (&__MSS_CTRL_U_BASE+&__MSS_CTRL_R5SS0_ROM_ECLIPSE) 0x7

PRINT "R5F ROM Eclipse"

PRINT ""

RETURN

)

R5F_SS0_CoreA_unhalt:

(

GOSUB Write_MMR (&__MSS_CTRL_U_BASE+&__MSS_CTRL_R5SS0_CORE0_HALT) 0x00000000

PRINT "R5FSS0_0 Released"

PRINT ""

RETURN

)

R5F_SS0_CoreB_unhalt:

(

GOSUB Write_MMR (&__MSS_CTRL_U_BASE+&__MSS_CTRL_R5SS0_CORE1_HALT) 0x00000000

PRINT "R5FSS0_1 Released"

PRINT ""

RETURN

)

R5F_SS1_CoreA_unhalt:

(

GOSUB Write_MMR (&__MSS_CTRL_U_BASE+&__MSS_CTRL_R5SS1_CORE0_HALT) 0x00000000

PRINT "R5FSS1_0 Released"

PRINT ""

RETURN

)

R5F_SS1_CoreB_unhalt:

(

GOSUB Write_MMR (&__MSS_CTRL_U_BASE+&__MSS_CTRL_R5SS1_CORE1_HALT) 0x00000000

PRINT "R5FSS1_1 Released"

PRINT ""

RETURN

)

Also can you tell me the relation between WFI and unhalting the core, Does unhating the core means that it will get out of WFI state?

Also I note that MSS_CTRL_R5SSx_COREx_HALT is always 0 (unhalted) for all cores no matter what (even I did not unhalt the core in the script) so do you have any idea why ?

I am asking these question because I am designing the OS and what I need that only the master core (R5SS0_0) runs first, all other cores are in halt/waiting state and then from Master core software I trigger the other cores to run.

But I cannot achieve this as I cannot understand the relation between halt/WFI and why the cores is always seems unhalted.

Hello Tareq,

Allow me some time to find accurate answers to your questions. In the mean time, would it be possible to link your complete .cmm file? This can be done by selecting "Insert" -> Image/video/file.

Regards,

Erik

Hello Tareq,

Thank you for sharing the .zip. I will be able to test and review it by tomorrow end of day.

The R5SS has three power states: Off, active, and standby. STANDBY mode refers to when there is a WFI or WFE instruction and the core hangs until there is work that wakes the core in the form of an IRQ.

The core HALT keeps the cores from fetching instructions when they come out of reset. The main use of this is to have the cores halted until the TCMs are loaded (when booting from the TCM), though halt could be used for other purposes.

Regards,

Erik

Hello Erik

Thank you for your reply and waiting your feedback regarding the sent scripts. Note that in addition to these scripts after that in master core in C code I try to unhalt other cores but nothing happens as I mentioned before.

So could unhating be used to release the other cores from the halt state ? Because In my case nothing works in c code to release the slave cores

Hello Tareq,

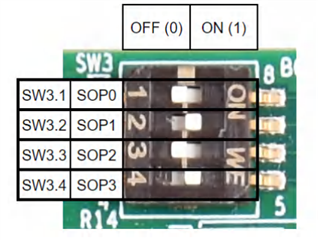

Can you try setting the bootmode to FLED mode? This is done by setting the SOP[0-3] as 0101.

By setting the bootmode to 0101 and changing syntax, the .cmm file that you provided worked. Here is the file with the syntax that was used:

https://e2e.ti.com/cfs-file/__key/communityserver-discussions-components-files/908/T32_5F00_PROG_5F00_C2_5F00_AM263x.cmm

Regards,

Erik

Additionally,

For your script to work in QSPI mode, then you need to implement a reset for "LOCKSTEP" mode and the code will work.

Lockstep reset that will work with QSPI bootmode:

R5F_SS0_Reset:

(

Var.NEWLOCAL unsigned int \r5fss0

GOSUB Write_MMR (&__MSS_RCM_U_BASE+&__MSS_RCM_R5SS0_RST2ASSERTDLY) 0x0

GOSUB Write_MMR (&__MSS_RCM_U_BASE+&__MSS_RCM_R5SS0_RST_WFICHECK) 0x00000707

GOSUB Read_MMR (&__MSS_CTRL_U_BASE+&__MSS_CTRL_R5SS0_STATUS_REG)

ENTRY &__V10

Var.Assign \r5fss0=&__V10

Var.IF (((\r5fss0)&(0x1<<0x8))!=(0x1<<0x8)) // if dual mode (not lockstep)

(

GOSUB Write_MMR (&__MSS_CTRL_U_BASE+&__MSS_CTRL_R5SS0_CONTROL) 0x707

GOSUB Write_MMR (&__MSS_CTRL_U_BASE+&__MSS_CTRL_R5SS0_CONTROL) 0x700

GOSUB Write_MMR (&__MSS_CTRL_U_BASE+&__MSS_CTRL_R5SS0_CONTROL) 0x70700

GOSUB Write_MMR (&__MSS_CTRL_U_BASE+&__MSS_CTRL_R5SS0_CONTROL) 0x00000000

)

ELSE

GOSUB Write_MMR (&__MSS_CTRL_U_BASE+&__MSS_CTRL_R5SS0_FORCE_WFI) 0x7

PRINT ""

PRINT ""

PRINT "***R5FSS0 Reset Complete***"

PRINT ""

RETURN

)

R5F_SS1_Reset:

(

Var.NEWLOCAL unsigned int \r5fss1

GOSUB Write_MMR (&__MSS_RCM_U_BASE+&__MSS_RCM_R5SS1_RST2ASSERTDLY) 0x0

GOSUB Write_MMR (&__MSS_RCM_U_BASE+&__MSS_RCM_R5SS1_RST_WFICHECK) 0x00000707

GOSUB Read_MMR (&__MSS_CTRL_U_BASE+&__MSS_CTRL_R5SS1_STATUS_REG)

ENTRY &__V11

Var.Assign \r5fss1=&__V11

Var.IF (((\r5fss1)&(0x1<<0x8))!=(0x1<<0x8)) // if dual mode (not lockstep)

(

GOSUB Write_MMR (&__MSS_CTRL_U_BASE+&__MSS_CTRL_R5SS1_CONTROL) 0x707

GOSUB Write_MMR (&__MSS_CTRL_U_BASE+&__MSS_CTRL_R5SS1_CONTROL) 0x700

GOSUB Write_MMR (&__MSS_CTRL_U_BASE+&__MSS_CTRL_R5SS1_CONTROL) 0x70700

GOSUB Write_MMR (&__MSS_CTRL_U_BASE+&__MSS_CTRL_R5SS1_CONTROL) 0x00000000

)

ELSE

GOSUB Write_MMR (&__MSS_CTRL_U_BASE+&__MSS_CTRL_R5SS1_FORCE_WFI) 0x7

PRINT ""

PRINT ""

PRINT "***R5FSS1 Reset Complete***"

PRINT ""

RETURN

)

Regards,

Erik

Hello Erik,

Thank you for your clear effort

Adding the script lines you have provided in last comment made the Core 1 (the slave core) to start directly after running the scripts.

But this is not the desired behaviour.

We wish that after running the scripts core 1 (slave core) is in halt state (not running) and Master core from SW we unhalt this slave core.

Seems that writing into MSS_CTRL_R5SS1_CORE0_HALT register is not doing anything in all cases.

I tried so many scenarios like trying to put the slave core in halt state by the scripts and unhating it through MSS_CTRL_R5SS1_CORE0_HALT in master core SW but seems this register not doing anything in any case.

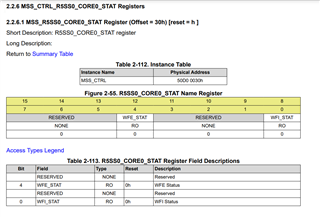

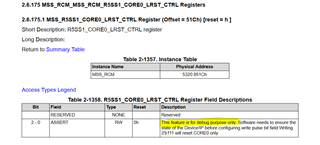

What actually worked for me is using MSS_R5SS1_CORE0_LRST_CTRL in Master core SW to reset R5SS1_CORE0 at certain point via writing 0x1 into MSS_R5SS1_CORE0_LRST_CTRL. Hence R5SS1_CORE0 start running as expected.

But the problem that in datasheet in mentions that MSS_R5SS1_CORE0_LRST_CTRL is for debug purpose only so I guess I cannot use it in my SW and deliver it to my customer to be used in production later on.

So if this register really for debug purpose only? or it is a documentation glitch ?

If it is really for debugging so that is its alternative ?

Hello Tareq,

Here is the expected flow for what you are trying to accomplish:

Core reset should not be needed but rather just unhalting the cores after loading the code.

Regards,

Erik