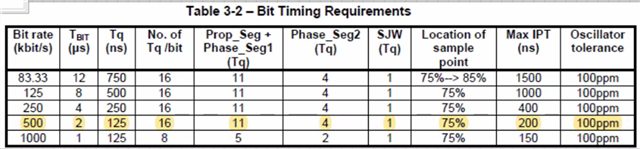

I'm unclear how to configure precise bit timings for CAN on the RM57L. The values highlighted in the table below are what I'm trying to achieve:

Available clock rates for VCLKA1 are: 15mhz, 70.313mhz, 10mhz, and 281.25mhz.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

I'm unclear how to configure precise bit timings for CAN on the RM57L. The values highlighted in the table below are what I'm trying to achieve:

Available clock rates for VCLKA1 are: 15mhz, 70.313mhz, 10mhz, and 281.25mhz.

Does this require that we generate a base 8mhz clock source to feed to VCLKA1? Can a PLL be adjusted or do we require an external source? My concern is that adjusting a PLL may interfere with the functionality of other modules that rely on it.

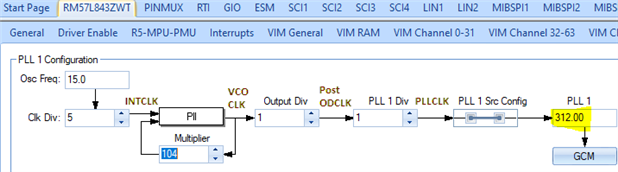

What is your PLL frequency? and OSC clock input frequency? You can set OSC as VLCKA1 source.

Is PLL=281.25 a special requirement for your application? RM57Lx can operate up to 330mHz

You can get VCLKA1=104 if PLL=312: