Hi,

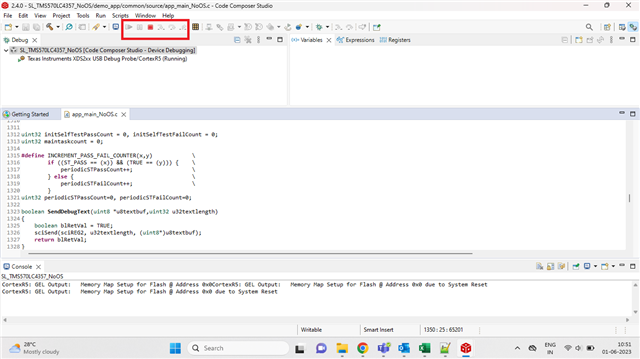

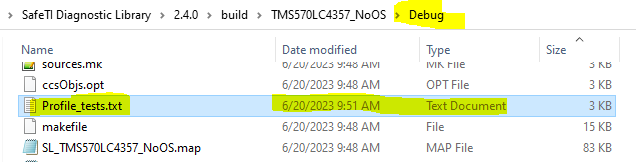

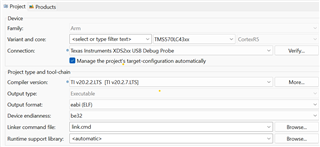

I am trying to run SAFETI library using demo code 2.4.0 in TMS570LC43x HERCULES DEVELOPMENT KIT.

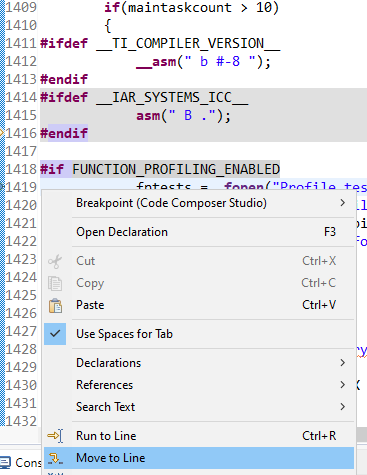

I am facing a problem that the code is stack and i did not find what happen in code. Is safety library is working or it is hang some where.

I am using TI safeTI diagnostic library. CCS IDE and TI sample/Demo code.

Note :- nERROR led is ON in developmnt kit.